芯片失效分析赵工 半导体工程师 2022-06-29 10:00 发表于北京

半导体制造工艺流程

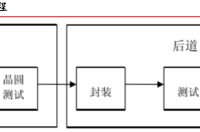

半导体制造的工艺过程由晶圆制造(Wafer Fabr ication)、晶圆测试(wafer Probe/Sorting)、芯片封装(Assemble)、测试(Test)以及后期的成品(Finish Goods)入库所组成。

半导体器件制作工艺分为前道和后道工序,晶圆制造和测试被称为前道(Front End)工序,而芯片的封装、测试及成品入库则被称为后道(Back End)工序,前道和后道一般在不同的工厂分开处理。

前道工序是从整块硅圆片入手经多次重复的制膜、氧化、扩散,包括照相制版和光刻等工序,制成三极管、集成电路等半导体元件及电极等,开发材料的电子功能,以实现所要求的元器件特性。

后道工序是从由硅圆片分切好的一个一个的芯片入手,进行装片、固定、键合联接、塑料灌封、引出接线端子、按印检查等工序,完成作为器件、部件的封装体,以确保元器件的可靠性,并便于与外电路联接。

半导体制造工艺和流程

晶圆制造

晶圆制造主要是在晶圆上制作电路与镶嵌电子元件(如电晶体、电容、逻辑闸等),是所需技术最复杂且资金投入最多的过程。以微处理器为例,其所需处理步骤可达数百道,而且所需加工机器先进且昂贵。虽然详细的处理程序是随着产品种类和使用技术的变化而不断变化,但其基本处理步骤通常是晶圆先经过适当的清洗之后,接着进行氧化及沉积处理,最后进行微影、蚀刻及离子植入等反复步骤,最终完成晶圆上电路的加工与制作。

晶圆测试

晶圆经过划片工艺后,表面上会形成一道一道小格,每个小格就是一个晶片或晶粒(Die),即一个独立的集成电路。在一般情况下,一个晶圆上制作的晶片具有相同的规格,但是也有可能在同一个晶圆上制作规格等级不同的晶片。晶圆测试要完成两个工作:一是对每一个晶片进行验收测试,通过针测仪器(Probe)检测每个晶片是否合格,不合格的晶片会被标上记号,以便在切割晶圆的时候将不合格晶片筛选出来;二是对每个晶片进行电气特性(如功率等)检测和分组,并作相应的区分标记。

芯片封装

首先,将切割好的晶片用胶水贴装到框架衬垫(Substrate)上;其次,利用超细的金属导线或者导电性树脂将晶片的接合焊盘连接到框架衬垫的引脚,使晶片与外部电路相连,构成特定规格的集成电路芯片(Bin);最后对独立的芯片用塑料外壳加以封装保护,以保护芯片元件免受外力损坏。塑封之后,还要进行一系列操作,如后固化(Post Mold Cure)、切筋(Trim)、成型(Form)和电镀(Plating)等工艺。

芯片测试

封装好的芯片成功经过烤机(Burn In)后需要进行深度测试,测试包括初始测试(Initial Test)和最后测试(Final Test)。初始测试就是把封装好的芯片放在各种环境下测试其电气特性(如运行速度、功耗、频率等),挑选出失效的芯片,把正常工作的芯片按照电气特性分为不同的级别。最后测试是对初始测试后的芯片进行级别之间的转换等操作。

成品入库

测试好的芯片经过半成品仓库后进入最后的终加工,包括激光印字、出厂质检、成品封装等,最后入库。

封装的基本定义和内涵

封装(packaging,PKG):主要是在半导体制造的后道工程中完成的。即利用膜技术及微细连接技术,将半导体元器件及其他构成要素在框架或基板上布置、固定及连接,引出接线端子,并通过塑性绝缘介质灌封固定,构成整体主体结构的工艺。

封装工程:是封装与实装工程及基板技术的总和。即将半导体、电子元器件所具有的电子的、物理的功能,转变为适用于机器或系统的形式,并使之为人类社会服务的科学技术,统称为电子封装工程。

封装一词用于电子工程的历史并不长。在真空电子管时代,将电子管等器件安装在管座上构成电路设备一般称为组装或装配,当时还没有封装这一概念。自从三极管、IC等半导体元件的出现,改变了电子工程的历史。一方面,这些半导体元件细小柔嫩;另一方面,其性能又高,而且多功能、多规格。为了充分发挥其功能,需要补强、密封、扩大,以便与外电路实现可靠地电气联接,并得到有效地机械支撑、绝缘、信号传输等方面的保护作用。“封装”的概念正是在此基础上出现的。

封装的功能

封装最基本的功能是保护电路芯片免受周围环境的影响(包括物理、化学的影响)。所以,在最初的微电子封装中,是用金属罐(Metal Can)作为外壳,用与外界完全隔离的、气密的方法,来保护脆弱的电子元件。但是,随着集成电路技术的发展,尤其是芯片钝化层技术的不断改进,封装的功能也在慢慢异化。

一般来说顾客所需要的并不是芯片,而是由芯片和PKG构成的半导体器件。PKG是半导体器件的外缘,是芯片与实装基板间的界面。因此无论PKG的形式如何,封装最主要的功能应是芯片电气特性的保持功能。

通常认为,半导体封装主要有电气特性的保持、芯片保护、应力缓和及尺寸调整配合四大功能,它的作用是实现和保持从集成电路器件到系统之间的连接,包括电学连接和物理连接。目前,集成电路芯片的I/0线越来越多,它们的电源供应和信号传送都是要通过封装来实现与系统的连接。芯片的速度越来越快,功率也越来越大,使得芯片的散热问题日趋严重,由于芯片钝化层质量的提高,封装用以保护电路功能的作用其重要性正在下降。

微电子封装的功能

芯片电气特性的保持功能

通过PKG的进步,满足不断发展的高性能、小型化、高频化等方面的要求,确保其功能性。

芯片保护功能

PKG的芯片保护功能很直观,保护芯片表面以及连接引线等,使在电气或物理等方面相当柔嫩的芯片免受外力损害及外部环境的影响。保证可靠性。

应力缓和功能

由于热等外部环境的影响或者芯片自身发热等都会产生应力,PKG缓解应力,防止发生损坏失效,保证可靠性。

尺寸调整配合(间距变化)功能

由芯片的微细引线间距调整到实装基板的尺寸间距,从而便于实装操作。例如,从亚微米(目前已小于 0.13μm)为特征尺寸的芯片到以10μm为单位的芯片电极凸点,再到以100μm为单位的外部引线端子,最后到以mm为单位的实装基板,都是通过PKG来实现的。在这里PKG起着由小到大、由难到易、由复杂到简单的变换作用。从而可使操作费用及资材费用降低,而且提高工作效率和可靠性。保证实用性或通用性。

封装的范围

微电子封装的三个层次

通常,从FAB厂制造的晶圆开始,可以将电子封装,按照制造的时间先后顺序分为三个层次。

微电子封装的三个层次

一级封装

一级封装是用封装外壳将芯片封装成单芯片组件(SCM)和多芯片组件(MCM)。半导体芯片和封装体的电学互联,通常有三种实现途径,引线键合(WB)、载带自动焊(TAB)和倒装焊(Flip Chip),一级封装的可以使用金属、陶瓷,塑料(聚合物)等包封材料。封装工艺设计需要考虑到单芯片或者多芯片之间的布线,与PCB节距的匹配,封装体的散热情况等。

二级封装

二级封装是印刷电路板的封装和装配,将一级封装的元器件组装到印刷电路板(PCB)上,包括板上封装单元和器件的互连,包括阻抗的控制、连线的精细程度和低介电常数材料的应用。除了特别要求外,这一级封装一般不单独加封装体,具体产品如计算机的显卡,PCI数据采集卡等都属于这一级封装。如果这一级封装能实现某些完整的功能,需要将其安装在同一的壳体中,例如Ni公司的USB数据采集卡,创新的外置USB声卡等。

三级封装

三级封装是将二级封装的组件查到同一块母板上,也就是关于插件接口、主板及组件的互连。这一级封装可以实现密度更高,功能更全组装,通常是一种立体组装技术。例如一台PC的主机,一个NI公司的PXI数据采集系统,汽车的GPS导航仪,这些都属于三级微电子封装的产品。

微电子封装是一个复杂的系统工程,类型多、范围广,涉及各种各样材料和工艺。可按几何维数将电子封装分解为简单的“点、线、面、体、块、板”等。

电子基板是半导体芯片封装的载体,搭载电子元器件的支撑,构成电子电路的基盘,按其结构可分为普通基板、印制电路板、模块基板等几大类。其中PCB在原有双面板、多层板的基础上,近年来又出现积层(build-up)多层板。模块基板是指新兴发展起来的可以搭载在PCB之上,以BGA、CSP、TAB、MCM为代表的封装基板(Package Substrate,简称PKG基板)。小到芯片、电子元器件,大到电路系统、电子设备整机,都离不开电子基板。近年来在电子基板中,高密度多层基板所占比例越来越大。

微电子封装所涉及的各个方面几乎都是在基板上进行或与基板相关。在电子封装工程所涉及的四大基础技术,即薄厚膜技术、微互连技术、基板技术、封接与封装技术中,基板技术处于关键与核心地位。随着新型高密度封装形式的出现,电子封装的许多功能,如电气连接,物理保护,应力缓和,散热防潮,尺寸过渡,规格化、标准化等,正逐渐部分或全部的由封装基板来承担。

微电子封装的范围涉及从半导体芯片到整机,在这些系统中,生产电子设备包括6个层次,也即装配的6个阶段。我们从电子封装工程的角度,按习惯一般称层次1为零级封装;层次2为一级封装;层次3为二级封装;层次4、5、6为三级封装。

电子封装的工程的六个阶段

层次1(裸芯片)

它是特指半导体集成电路元件(IC芯片)的封装,芯片由半导体厂商生产,分为两类,一类是系列标准芯片,另一类是针对系统用户特殊要求的专用芯片,即未加封装的裸芯片(电极的制作、引线的连接等均在硅片之上完成)。

层次2(封装后的芯片即集成块)

分为单芯片封装和多芯片封装两大类。前者是对单个裸芯片进行封装,后者是将多个裸芯片装载在多层基板(陶瓷或有机)上进行气密性封装构成MCM。

层次3(板或卡)

它是指构成板或卡的装配工序。将多个完成层次2的单芯片封装和MCM,实装在PCB板等多层基板上,基板周边设有插接端子,用于与母板及其它板或卡的电气连接。

层次4(单元组件)

将多个完成层次3的板或卡,通过其上的插接端子搭载在称为母板的大型PCB板上,构成单元组件。

层次5(框架件)

它是将多个单元构成(框)架,单元与单元之间用布线或电缆相连接。

层次6(总装、整机或系统)

它是将多个架并排,架与架之间由布线或电缆相连接,由此构成大型电子设备或电子系统。

从硅圆片制作开始,微电子封装可分为0、1、2、3四个等级,涉及上述六个层次,封装基板(PKG基板或Substrate)技术现涉及1、2、3三个等级和2~5的四个层次。

封装基板主要研究前3个级别的半导体封装(1、2、3级封装),0级封装暂与封装基板无关,因此封装基板一般是指用于1级2级封装的基板材料,母板(或载板)、刚挠结合板等用于三级封装。

零级封装

裸芯片电极的制作、引线的连接等均在硅片之上完成,暂与基板无关。

一级封装

一级封装经0级封装的单芯片或多芯片在封装基板(普通基板、多层基板、HDI基板)上的封装,构成集成电路模块(或元件)。即芯片在各类基板(或中介板)上的装载方式。

二级封装

二级封装集成电路(IC元件或IC块)片在封装基板(普通基板、多层基板、HDI基板)上的封装,构成板或卡。即各种实装方式(二级封装或一级加二级封装)。后续谈到的的DIP、PGA属于DIP封型,GFP、BGA、CSP等属于SMT实装型,这些都属于二级封装。

三级封装

三级封装包含4、5、6三个层次。即将多个完成层次3的板或卡,通过其上的插接端子搭载在称为母板(或载板)的大型PCB板上,构成单元组件(此层次也是实装方式之一);或是将多个单元构成架,单元与单元之间用布线(刚挠PCB)或电缆相连接;或是将多个架并排,架与架之间由布线(刚挠PCB)或电缆相连接,由此构成大型电子设备或系统(此两个层次称为装联)。

传统集成电路(IC)封装的主要生产过程

IC的封装工艺流程可分为晶圆切割、晶圆粘贴、金线键合、塑封、激光打印、切筋打弯、检验检测等步骤。

传统半导体封装的七道工序

晶圆切割

首先将晶片用薄膜固定在支架环上,这是为了确保晶片在切割时被固定住,然后把晶圆根据已有的单元格式被切割成一个一个很微小的颗粒,切割时需要用去离子水冷却切割所产生的温度,而本身是防静电的。

晶圆粘贴

晶圆粘贴的目的将切割好的晶圆颗粒用银膏粘贴在引线框架的晶圆上,用粘合剂将已切下来的芯片贴装到引线框架的中间焊盘上。通常是环氧(或聚酰亚胺)用作为填充物以增加粘合剂的导热性。

金线键合

金线键合的目的是将晶圆上的键合压点用极细的金线连接到引线框架上的内引脚上,使得晶圆的电路连接到引脚。通常使用的金线的一端烧成小球,再将小球键合在第一焊点。然后按照设置好的程序拉金线,将金线键合在第二焊点上。

塑封

将完成引线键合的芯片与引线框架置于模腔中,再注入塑封化合物环氧树脂用于包裹住晶圆和引线框架上的金线。这是为了保护晶圆元件和金线。塑封的过程分为加热注塑,成型二个阶段。塑封的目的主要是:保护元件不受损坏;防止气体氧化内部芯片;保证产品使用安全和稳定。

激光打印

激光打印是用激光射线的方式在塑封胶表面打印标识和数码。包括制造商的信息,器件代码,封装日期,可以作为识别和可追溯性。

切筋打弯

将原来连接在一起的引线框架外管脚切断分离,并将其弯曲成设计的形状,但不能破坏环氧树脂密封状态,并避免引脚扭曲变形,将切割好的产品装入料管或托盘便于转运。

检验

检验检查产品的外观是否能符合设计和标准。常见的的测试项目包括:打印字符是否清晰、正确,引脚平整性、共面行,引脚间的脚距,塑封体是否损伤、电性能及其它功能测试等。

半导体封装技术和工艺

半导体封装技术

芯片封装的实质:

传统意义的芯片封装一般指安放集成电路芯片所用的封装壳体,它同时可包含将晶圆切片与不同类型的芯片管脚架及封装材料形成不同外形的封装体的过程。从物理层面看,它的基本作用为:为集成电路芯片提供稳定的安放环境,保护芯片不受外部恶劣条件(例如灰尘,水气)的影响。从电性层面看,芯片封装同时也是芯片与外界电路进行信息交互的链路,它需要在芯片与外界电路间建立低噪声、低延迟的信号回路。

然而不论封装技术如何发展,归根到底,芯片封装技术都是采用某种连接方式把晶圆切片上的管脚与引线框架以及封装壳或者封装基板上的管脚相连构成芯片。而封装的本质就是规避外界负面因素对芯片内部电路的影响,同时将芯片与外部电路连接,当然也同样为了使芯片易于使用和运输。

芯片封装技术越来越先进,管角间距越来越小,管脚密度却越来越高,芯片封装对温度变化的耐受性越来越好,可靠性越来越高。另外一个重要的指标就是看芯片与封装面积的比例。

此外,封装技术中的一个主要问题是芯片占用面积,即芯片占用的印刷电路板(PCB)的面积。从早期的DIP封装,当前主流的CSP封装,芯片与封装的面积比可达1:1.14,已经十分接近1:1的理想值。而更先进MCM到SiP封装,从平面堆叠到垂直堆叠,芯片与封装的面积相同的情况下进一步提高性能。

各种常用封装管壳

封装管壳内部

封装技术工艺发展历程:

半导体封装技术的发展历史可划分为三个阶段。

半导体封装技术的发展历史

第一阶段(20世纪70年代之前)

以通孔插装型封装为主;典型的封装形式包括最初的金属圆形(TO型)封装,以及后来的陶瓷双列直插封装(CDIP)、陶瓷-玻璃双列直插封装(Cer DIP)和塑料双列直插封装(PDIP)等;其中的PDIP,由于其性能优良、成本低廉,同时又适于大批量生产而成为这一阶段的主流产品。

第二阶段(20世纪80年代以后)

从通孔插装型封装向表面贴装型封装的转变,从平面两边引线型封装向平面四边引线型封装发展。表面贴装技术被称为电子封装领域的一场革命,得到迅猛发展。与之相适应,一些适应表面贴装技术的封装形式,如塑料有引线片式裁体(PLCC)、塑料四边引线扁平封装(PQFP)、塑料小外形封装(PSOP)以及无引线四边扁平封装(PQFN)等封装形式应运而生,迅速发展。其中的PQFP,由于密度高、引线节距小、成本低并适于表面安装,成为这一时期的主导产品。

第三阶段(20世纪90年代以后)

半导体发展进入超大规模半导体时代,特征尺寸达到0.18-0.25µm,要求半导体封装向更高密度和更高速度方向发展。因此,半导体封装的引线方式从平面四边引线型向平面球栅阵列型封装发展,引线技术从金属引线向微型焊球方向发展。

在此背景下,焊球阵列封装(BGA)获得迅猛发展,并成为主流产品。BGA按封装基板不同可分为塑料焊球阵列封装(PBGA),陶瓷焊球阵列封装(CBGA),载带焊球阵列封装(TBGA),带散热器焊球阵列封装(EBGA),以及倒装芯片焊球阵列封装(FC-BGA)等。

为适应手机、笔记本电脑等便携式电子产品小、轻、薄、低成本等需求,在BGA的基础上又发展了芯片级封装(CSP);CSP又包括引线框架型CSP、柔性插入板CSP、刚性插入板CSP、园片级CSP等各种形式,目前处于快速发展阶段。

同时,多芯片组件(MCM)和系统封装(SiP)也在蓬勃发展,这可能孕育着电子封装的下一场革命性变革。MCM按照基板材料的不同分为多层陶瓷基板MCM(MCM-C)、多层薄膜基板MCM(MCM-D)、多层印制板MCM(MCM-L)和厚薄膜混合基板MCM(MCM-C/D)等多种形式。SiP是为整机系统小型化的需要,提高半导体功能和密度而发展起来的。SiP使用成熟的组装和互连技术,把各种集成电路如CMOS电路、GaAs电路、SiGe电路或者光电子器件、MEMS器件以及各类无源元件如电阻、电容、电感等集成到一个封装体内,实现整机系统的功能。

目前,半导体封装处于第三阶段的成熟期与快速增长期,以BGA/CSP等主要封装形式开始进入规模化生产阶段。同时,以SiP和MCM为主要发展方向的第四次技术变革处于孕育阶段。

半导体封装材料

半导体元件的封接或封装方式分为气密性封装和树脂封装两大类,气密性封装又可分为金属封装、陶瓷封装和玻璃封装。封接和封装的目的是与外部温度、湿度、气氛等环境隔绝,除了起保护和电气绝缘作用外,同时还起向外散热及应力缓和作用。一般来说,气密性封装可靠性高,但价格也高。目前由于封装技术及材料的改进,树脂封装已占绝对优势,但在有些特殊领域(军工、航空、航天、航海等),气密性封装是必不可少的。

按封装材料可划分为:金属封装、陶瓷封装(C)、塑料封装(P)。采用前两种封装的半导体产品主要用于航天、航空及军事领域,而塑料封装的半导体产品在民用领域得到了广泛的应用。目前树脂封装已占世界集成电路封装市场的98%,97%以上的半导体器件的封装都采用树脂封装,在消费类电路和器件领域基本上是树脂封装一统天下,而90%以上的塑封料是环氧树脂塑封料和环氧液体灌封料。

芯片电学(零级封装)互连:

在一级封装中,有个很重要的步骤就是将芯片和封装体(进行电学互连的过程,通常称为芯片互连技术或者芯片组装。为了凸显其重要性,有些教科书也将其列为零级封装。也就是将芯片上的焊盘或凸点与封装体通常是引线框架用金属连接起来)。在微电子封装中,半导体器件的失效约有一是由于芯片互连引起的,其中包括芯片互连处的引线的短路和开路等,所以芯片互连对器件的可靠性非常重要。

常见的芯片电学互连有三种方式,分别是引线键合,载带自动焊和倒装焊。

通常,TAB和FC虽然互连的电学性能要比好,但是都需要额外的设备。因此,对于I/O数目较少的芯片,TAB和FC成本很高,另外,在3D封装中,由于芯片堆叠,堆叠的芯片不能都倒扣在封装体上,只能通过WB与封装体之间进行互连。基于这些原因,到目前为止,WB一直是芯片互连的主流技术,在芯片电学互连中占据非常重要的地位。

芯片电学互连(零级封装)的三种方式

引线键合(WB)

引线键合(WB)是将芯片焊盘和对应的封装体上焊盘用细金属丝一一连接起来,每次连接一根,是最简单的一种芯片电学互连技术,按照电气连接方式来看属于有线键合。

载带自动焊(TAB)

载带自动焊(TAB)是一种将IC安装和互连到柔性金属化聚合物载带上的IC组装技术。载带内引线键合到IC上,外引线键合到常规封装或者PCB上,整个过程均自动完成,因此,效率比要高。按照电气连接方式来看属于无线键合方法。

倒装焊(FC)

倒装焊(FC)是指集成电路芯片的有源面朝下与载体或基板进行连接。芯片和基板之间的互连通过芯片上的凸点结构和基板上的键合材料来实现。这样可以同时实现机械互连和电学互连。同时为了提高互连的可靠性,在芯片和基板之间加上底部填料。对于高密度的芯片,倒装焊不论在成本还是性能上都有很强的优势,是芯片电学互连的发展趋势。按照电气连接方式来看属于无线键合方法。

依据封装管脚的排布方式、芯片与PCB板连接方式以及发展的时间先后顺序,半导体封装可划分为PTH封装(Pin-Through-Hole)和SMT封装(Surface-Mount-Technology)二大类,即通常所称的插孔式(或通孔式)和表面贴装式。

针脚插装技术(PTH):

针脚插装封装,顾名思义即在芯片与目标板的连接过程中使用插装方式,古老而经典DIP封装即属于该种封装形式。在早期集成电路中由于芯片集成度不高,芯片工作所需的输入/输出管脚数较少,所以多采用该种封装形式。DIP封装有两种衍生封装形式,即为:SiP和ZIP,只是为适应不同的应用领域,对传统DIP封装在封装壳管脚排布和形状上略有改进。

PTH封装示意图

表面贴装封装(SMT):

PTH封装在机械连接强度上的优势毋庸质疑,但同时也带来一些负面效应。PTH封装中使用的贯通孔将大量占用PCB板有效布线面积,因此目前主流的PCB板设计中多使用表面贴片封装。

小型塑封晶体管(Small Outline Transistor,SOT)

小引出线封装(Smal lOutline Package,SOP)

四方扁平无引线封装(Quad Flat No-lead Package,QFN)

薄小缩小外形封装(Thin Small Shrink Outline Package,TSSOP)

方型扁平式封装(Quad Flat Package,QFP)

方形扁平无引脚封装(QFN)

从SOT到QFN,芯片封装壳支持的管脚数越来越多,芯片封装壳的管角间距越来越小。

表面贴片封装方式的优点在于芯片封装的尺寸大大下降,芯片封装的管脚密度大大提升,与PTH封装具有相同管脚数量时,表面贴片封装的封装尺寸将远小于PTH封装。表面贴片封装只占用PCB板表层布线空间,在使用多层布线工艺时,封装占用的有效布线面积大大下降,可以大大提高PCB板布线密度和利用率。

BGA:

封装伴随着芯片集成度不断提高,为使芯片实现更复杂的功能,芯片所需的输入/输出管脚数量也进一步提升,面对日趋增长的管脚数量和日趋下降的芯片封装尺寸,微电子封装提出了一种新的封装形式BGA封装。

BGA封装的底部按照矩阵方式制作引脚,引脚的形状为球形,在封装壳的正面装配芯片,有时也会将BGA芯片与球形管脚放在基板的同一侧。BGA封装是大规模集成电路的一种常用封装形式。BGA封装按照封装壳基板材质的不同,可分为三类:塑料BGA、陶瓷BGA、载带BGA。

BGA封装具有以下共同特点:

芯片封装的失效率较低;

管脚共面较好,减少管脚共面损害带来的焊接不良;

BGA引脚为焊料值球,不存在引脚变形问题;

BGA封装引脚较短,输入/输出信号链路大大缩短,减少了因管脚长度引入的电阻/电容/电感效应,改善了封装壳的寄生参数;

BGA球栅阵列与PCB板接触点较多,接触面积较大,有利于芯片散热,BGA封装有利提高封装的封装密度。

BGA封装使用矩阵形式的管脚排列,相对于传统的贴片封装,在相同管脚数量下,BGA封装的封装尺寸可以做的更小,同时也更节省PCB板的布线面积。

芯片级(CSP)封装技术

CSP定义

根据J-STD-012标准的定义,CSP是指封装尺不超过裸芯片1.2倍的一种先进的封装形式。一般认为CSP技术是在对现有的芯片封装技术,尤其是对成熟的BGA封装技术做进一步技术提升的过程中,不断将各种封装尺寸进一步小型化而产生的一种封装技术。

CSP技术可以确保超大规模集成电路在高性能、高可靠性的前提下,以最低廉的成本实现封装的尺寸最接近裸芯片尺寸。与QFP封装相比,CSP封装尺寸小于管脚间距为0.5mm的QFP封装的1/10;与BGA封装相比,CSP封装尺寸约为BGA封装的1/3。

当封装尺寸固定时,若想进一步提升管脚数,则需缩小管脚间距。受制于现有工艺,不同封装形式存在工艺极限值。如BGA封装矩阵式值球最高可达1000个,但CSP封装可支持超出2000的管脚。

CSP的主要结构有内芯芯片、互连层、焊球(或凸点、焊柱)、保护层等几大部分,芯片与封装壳是在互连层实现机械连接和电性连接。其中,互连层是通过载带自动焊接或引线键合、倒装芯片等方法,来实现芯片与焊球之间的内部连接,是CSP关键组成部分。

目前有多种符合CSP定义的封装结构形式,其特点有:

CSP的芯片面积与封装面积之比与1:1的理想状况非常接近,绝对尺寸为32mm2,相当于BGA的三分之一和TSOP的六分之一,即CSP可将内存容量提高3~6倍之多。

测试结果显示,CSP可使芯片88.4%的工作热量传导至PCB,热阻为35℃/W-1,而TSOP仅能传导总热量的71.3%,热阻为40℃/W-1。

CSP所采用的中心球形引脚形式能有效地缩短信号的传导距离,信号衰减也随之减少,芯片的抗干扰、抗噪性能更强,存取时间比BGA减少15%~20%,完全能适应DDRⅡ,DRDRAM等超高频率内存芯片的实际需要。

CSP可容易地制造出超过1000根信号引脚数,即使最复杂的内存芯片都能封装,在引脚数相同的情况下,CSP的组装远比BGA容易。CSP还可进行全面老化、筛选、测试,且操作、修整方便,能获得真正的KGD(Known GoodDie已知合格芯片)芯片。

CSP封装形式主要有如下分类

芯片级封装的主要类型:

柔性基片CSP

顾名思义是采用柔性材料制成芯片载体基片,在塑料薄膜上制作金属线路,然后将芯片与之连接。柔性基片CSP产品,芯片焊盘与基片焊盘间的连接方式可以是倒装键合、TAB键合、引线键合等多种方式,不同连接方式封装工艺略有差异。

硬质基片CSP

其芯片封装载体基材为多层线路板制成,基板材质可为陶瓷或层压树脂板。

引线框架CSP

技术是由日本的Fujitsu公司首先研发成功,使用与传统封装相类似的引线框架来完成CSP封装。引线框架CSP技术使用的引线框架与传统封装引线框架的区别在于该技术使用的引线框架尺寸稍小,厚度稍薄。

微小模塑型CSP

是由日本三菱电机公司提出的一种CSP封装形式。芯片管脚通过金属导线与外部焊球连接,整个封装过程中不需使用额外引线框架,封装内芯片与焊球连接线很短,信号品质较好。

晶圆级CSP

由ChipScale公司开发。其技术特点在于直接使用晶圆制程完成芯片封装。与其他各类CSP相比,晶圆级CSP所有工艺使用相同制程完成,工艺稳定。基于上述优点,晶圆级CSP封装有望成为未来的CSP封装的主流方式。

先进封装

堆叠封装:

堆叠封装分类:

堆叠封装技术是一种对两个以上芯片(片芯、籽芯)、封装器件或电路卡进行机械和电气组装的方法,在有限的空间内成倍提高存储器容量,或实现电子设计功能,解决空间、互连受限问题。

堆叠封装分为定制堆叠和标准商业堆叠两大类型:前者是通过芯片层次工艺高密度化,其设计和制造成本相对较高;后者采用板卡堆叠、柔性电路连接器联接、封装后堆叠、芯片堆叠式封装等方式,其成本比采用单芯片封装器件的存储器模块高平均15%~20%。应该看到,芯片堆叠式封装的成本效率最高,在一个封装体内有2~5层芯片堆叠,从而能在封装面积不变的前提下,有效利用立体空间提高存储容量,主要用于DRAM、闪存和SRAM。另外,通过堆叠TSOP可分别节约50%或77%的板级面积。

堆叠封装的特点:

芯片堆叠封装主要强调用于堆叠的基本“元素”是晶圆切片。

多芯片封装、堆叠芯片尺寸封装、超薄堆叠芯片尺寸封装等均属于芯片堆叠封装的范畴。芯片堆叠封装技术优势在于采用减薄后的晶圆切片可使封装的高度更低。

堆叠封装有两种不同的表现形式,即PoP堆叠(Package on Package,PoP)和PiP堆叠(Package in Package Stacking,PiP)。

PoP堆叠使用经过完整测试且封装完整的芯片,其制作方式是将完整的单芯片或堆叠芯片堆叠到另外一片完整单芯片或堆叠芯片的上部。其优势在于参与堆叠的基本“元素”为成品芯片,所以该技术理论上可将符合堆叠要求的任意芯片进行堆叠。

PiP堆叠使用经过简单测试的内部堆叠模块和基本组装封装作为基本堆叠模块,但受限于内部堆叠模块和基本组装封装的低良率,PiP堆叠成品良率较差。但PiP的优势也十分明显,即在堆叠中可使用焊接工艺实现堆叠连接,成本较为低廉。

PoP封装外形高度高于PiP封装,但是装配前各个器件可以单独完整测试,封装后的成品良率较好。

3D封装可以在更小,更薄的封装壳内封装更多的芯片。按照结构3D封装可分为芯片堆叠封装和封装堆叠封装。

晶圆级封装(WLP)

WLP的优势:

晶圆级封装(WLP)就是在封装过程中大部分工艺过程都是对晶圆(大圆片)进行操作,对晶圆级封装(WLP)的需求不仅受到更小封装尺寸和高度的要求,还必须满足简化供应链和降低总体成本,并提高整体性能的要求。

晶圆级封装提供了倒装芯片这一具有极大优势的技术,倒装芯片中芯片面朝下对着印刷电路板(PCB),可以实现最短的电路径,这也保证了更高的速度,降低成本是晶圆级封装的另一个推动力量。

器件采用批量封装,整个晶圆能够实现一次全部封装。在给定晶片上封装器件的成本不会随着每片晶片的裸片数量而改变,因为所有工艺都是用掩模工艺进行的加成和减法的步骤。

WLP技术的两种类型:

总体来说,WLP技术有两种类型:“扇入式”(fan-in)和“扇出式”(fan-out)晶圆级封装。

传统扇入WLP在晶圆未切割时就已经形成。在裸片上,最终的封装器件的二维平面尺寸与芯片本身尺寸相同。器件完全封装后可以实现器件的单一化分离(singulation)。因此,扇入式WLP是一种独特的封装形式,并具有真正裸片尺寸的显著特点。具有扇入设计的WLP通常用于低输入/输出(I/O)数量(一般小于400)和较小裸片尺寸的工艺当中。

另一方面,随着封装技术的发展,逐渐出现了扇出式WLP。扇出WLP初始用于将独立的裸片重新组装或重新配置到晶圆工艺中,并以此为基础,通过批量处理、构建和金属化结构,如传统的扇入式WLP后端处理,以形成最终封装。

扇出式WLP可根据工艺过程分为芯片先上(Die First)和芯片后上(Die Last),芯片先上工艺,简单地说就是先把芯片放上,再做布线(RDL),芯片后上就是先做布线,测试合格的单元再把芯片放上去,芯片后上工艺的优点就是可以提高合格芯片的利用率以提高成品率,但工艺相对复杂。eWLB就是典型的芯片先上的Fan out工艺,长电科技星科金朋的Fan-out,安靠(Amkor)的葡萄牙工厂均采用的芯片先上的工艺。TSMC的INFO也是芯片先上的Fan-out产品。安靠和ASE也都有自己成熟的芯片后上的Fan-out工艺。

在电子设备的发展历史中,WLP封装技术的推广产生了很多全新的产品。

例如得益于WLP的使用,摩托罗拉能够推出其RAZR手机,该手机也是其推出时最薄的手机。最新型号的iPhone采用了超过50颗WLP,智能手机是WLP发展的最大推动力。

随着金线价格的上涨,一些公司也正在考虑采用WLP作为低成本替代方案,而不是采用引线键合封装,尤其是针对更高引脚数的器件。最近几年中,WLP也已经被广泛用于图像传感器的应用中。目前,硅通孔(TSV)技术已被纳入用于封装图像传感器的WLP解决方案。其他更新的封装技术也在逐渐发展,并与现有的WLP技术进行整合,例如三维(3D)集成技术。

2.5D/3D先进封装集成工艺

新兴的2.5D和3D技术有望扩展到倒装芯片和晶圆级封装工艺中。通过使用硅中介层(Interposers)和硅通孔(TSV)技术,可以将多个芯片进行垂直堆叠。TSV堆叠技术实现了在不增加IC平面尺寸的情况下,融合更多的功能到IC中,允许将更大量的功能封装到IC中而不必增加其平面尺寸,并且硅中介层用于缩短通过集成电路中的一些关键电通路来实现更快的输入和输出。因此,使用先进封装技术封装的应用处理器和内存芯片将比使用旧技术封装的芯片小约30%或40%,比使用旧技术封装的芯片快2~3倍,并且可以节省高达40%或者更多的功率。

2.5D和3D技术的复杂性以及生产这些芯片的IC制造商(Fab)和外包封装/测试厂商的经济性意味着IDM和代工厂仍需要处理前端工作,而外包封装/测试厂商仍然最适合处理后端过程,比如通过露出、凸点、堆叠和测试。外包封装/测试厂商的工艺与生产主要依赖于内插件的制造,这是一种对技术要求较低的成本敏感型工艺。

三维封装可以更高效地利用硅片,达到更高的“硅片效率”。硅片效率是指堆叠中的总基板面积与占地面积的比率。因此,与其他2D封装技术相比,3D技术的硅效率超过了100%。而在延迟方面,需要通过缩短互连长度来减少互连相关的寄生电容和电感,从而来减少信号传播延迟。而在3D技术中,电子元件相互靠得很近,所以延迟会更少。相类似,3D技术在降低噪声和降低功耗方面的作用在于减少互连长度,从而减少相关寄生效应,从而转化为性能改进,并更大程度的降低成本。此外,采用3D技术在降低功耗的同时,可以使3D器件以更高的频率运行,而3D器件的寄生效应、尺寸和噪声的降低可实现更高的每秒转换速率,从而提高整体系统性能。

3D集成技术作为2010年以来得到重点关注和广泛应用的封装技术,通过用3D设备取代单芯片封装,可以实现相当大的尺寸和重量降低。这些减少量的大小部分取决于垂直互连密度和可获取性(accessibility)和热特性等。据报道,与传统封装相比,使用3D技术可以实现40~50倍的尺寸和重量减少。

举例来说,德州仪器(TI)的3D裸片封装与离散和平面封装(MCM)之间的体积和重量相比,可以减少5~6倍的体积,并且在分立封装技术上可以减少10~20倍。此外,与MCM技术相比,重量减少2~13倍,与分立元件相比,重量减少3~19倍。此外,封装技术中的一个主要问题是芯片占用面积,即芯片占用的印刷电路板(PCB)的面积。在采用MCM的情况下,芯片占用面积减少20%~90%,这主要是因为裸片的使用。

系统级封装SiP技术

SiP是半导体封装领域的最高端的一种新型封装技术,将一个或多个IC芯片及被动元件整合在一个封装中,综合了现有的芯核资源和半导体生产工艺的优势。SiP是为整机系统小型化的需要,提高半导体功能和密度而发展起来的。SiP使用成熟的组装和互连技术,把各种集成电路如CMOS电路、GaAs电路、SiGe电路或者光电子器件、MEMS器件以及各类无源元件如电阻、电容、电感等集成到一个封装体内。

自从1960年代以来,集成电路的封装形式经历了从双列直插、四周扁平封装、焊球阵列封装和圆片级封装、芯片尺寸封装等阶段。而小型化、轻量化、高性能、多功能、高可靠性和低成本的电子产品的总体发展趋势使得单一芯片上的晶体管数目不再是面临的主要挑战,而是要发展更先进的封装及时来满足产品轻、薄、短、小以及与系统整合的需求,这也使得在独立的系统(芯片或者模块)内充分实现芯片的功能成为需要克服的障碍。这样的背景是SiP逐渐成为近年来集成电路研发机构和半导体厂商的重点研究对象。SiP作为一种全新的集成方法和封装技术,具有一系列独特的技术优势,满足了当今电子产品更轻、更小和更薄的发展需求,在微电子领域具有广阔的应用市场和发展前景。

SiP/SoP

近年来,随着消费类电子产品(尤其是移动通信电子产品)的飞速发展,使得三维高密度系统级封装(3D SiP,System in Package/SoP,System on Package)成为了实现高性能、低功耗、小型化、异质工艺集成、低成本的系统集成电子产品的重要技术方案,国际半导体技术路线(ITRS)已经明确SiP/SoP将是未来超越摩尔(More than Moore)定律的主要技术。SiP从结构方向上可以分为两类基本的形式,一类是多块芯片平面排布的二维封装结构(2D SiP),另一类是芯片垂直叠装的三维封装/集成结构(3D SiP)。

在2DSiP结构中,芯片并排水平贴装在基板上的,贴装不受芯片尺寸大小的限制,工艺相对简单和成熟,但其封装面积相应地比较大,封装效率比较低。3DSiP可实现较高的封装效率,能最大限度地发挥SiP的技术优势,是实现系统集成的最为有效的技术途径,实际上涉及多种先进的封装技术,包括封装堆叠(PoP)、芯片堆叠(CoC)、硅通孔(TSV)、埋入式基板(Embedded Substrate)等,也涉及引线键合、倒装芯片、微凸点等其他封装工艺。3DSiP的基本概念正是将可能实现的多种功能集成于一个系统中,包括微处理器、存储器、模拟电路、电源转化模块、光电器件等,还可能将散热通道等部件也集成在封装中,最大程度的体现SiP的技术优势。

系统级封装技术可以解决目前我们遇到的很多问题,其优势也是越来越明显,如产品设计的小型化、功能丰富化、产品可靠性等,产品制造也越来越极致,尤为重要的是,提高了生产效率,并大幅降低了生产成本。当然,难点也是存在的,系统级封装的实现,需要各节点所有技术,而不是某一技术所能实现的,这对封装企业来说,就需要有足够的封装技术积累及可靠的封装平台支撑,如高密度模组技术、晶圆级封装技术等。

多芯片组件(MCM)

多芯片组件(MCM)属于系统级封装,是电子封装技术层面的大突破。MCM是指一个封装体中包含通过基板互连起来,共同构成整个系统的封装形式的两个或两个以上的芯片。并为组件中的所有芯片提供信号互连、I/O管理、热控制、机械支撑和环境保护等条件。根据所用多层布线基板的类型不同,MCM可分为叠层多芯片组件(MCM-L)、陶瓷多芯片组件(MCM-C)、淀积多芯片组件(MCM-D)以及混合多芯片组件(MCM–C/D)等。

多芯片封装技术从某种程度上而言可以减少由芯片功能过于复杂带来的研发压力。由于多芯片方案可以使用完全独立的成熟芯片搭建系统,无论从成本角度还是从技术角度考虑,单芯片方案的研发难度远大于多芯片方案。现阶段产品发展的趋势为小型化便携式产品,产品外部尺寸的缩小将压缩芯片可用布线空间,这就迫使封装技术改善封装的尺寸来适应更小型的产品。

价值量最大的耗材

传统的半导体封装,是使用引线框架作IC导通线路与支撑IC的载具,它连接引脚于引线框架的两旁或四周。随着半导体封装技术的发展,当引脚数增多(超过300个引脚),传统的QFP等封装形式已对其发展有所限制。这样,在20世纪90年代中期,以BGA、CSP为代表的新型半导体封装形式问世,随之也产生了一种半导体芯片封装必要的新载体,这就是半导体封装基板(IC Package Substrate,又称为半导体封装载板)。

IC封装基板起到在芯片与常规印制电路板(多为主板、母板、背板)的不同线路之间提供电气连接(过渡)的作用,同时为芯片提供保护、支撑、散热的通道,以及达到符合标准安装尺寸的功效。可实现多引脚化、缩小封装产品面积、改善电性能及散热性、实现高密度化等是它的突出优点。因此以BGA、CSP以及倒装芯片(FC,FpilChpi)等形式的半导体封装基板,在近年来的应用领域得到迅速扩大,广为流行。

基于在半导体封装中充分运用高密度多层基板技术方面,以及降低封装基板的制造成本方面(封装基板成本以BGA为例约占40%~50%,在FC基板制造成本方面它约70%~80%)的需求,半导体封装基板已成为一个国家、一个地区在发展微电子产业中的重要“武器”之一。

从芯片支撑材料角度来看半导体封装技术分类

目前普遍使用的封装技术有很多,可分为以下几类:

芯片的封装种类太过繁杂,为了方便理解,我们将分类方式简化,以封装过程中使用的承载晶圆或芯片的耗材的不同来份额里,半导体封装技术可以分为引线框封装、裸芯片封装/晶圆级封装和嵌入式封装三类。

芯片封装技术分类

引线框架+封装壳

我们把使用传统封装壳的封装技术和使用封装基材的封装技术归为一类,总体称为封装中使用封装壳的封装技术。

嵌入式封装

嵌入式芯片(Embedded Component Packaging EPC),封装与大多数封装类型并不相同。一般来说,在许多集成电路封装中,器件位于基板的顶部,基板充当器件与封装板间“桥梁”的角色。

裸芯片封(组)装装技术/晶圆级封装(WLP)

二级封装是印刷电路板的封装和装配,将一级封装的元器件组装到印刷电路板(PCB)上,包括板上封装单元和器件的互连,包括阻抗的控制、连线的精细程度和低介电常数材料的应用。除了特别要求外,这一级封装一般不单独加封装体,具体产品如计算机的显卡,PCI数据采集卡等都属于这一级封装。如果这一级封装能实现某些完整的功能,需要将其安装在同一的壳体中,例如Ni公司的USB数据采集卡,创新的外置USB声卡等。

引线框架封装(LeadframePackages)

传统的IC封装是采用导线框架作为IC导通线路与支撑IC的载具,它连接引脚于导线框架的两旁或四周。随着IC封装技术的发展,引脚数量的增多(超过300以上个引脚)、、线密度的增大、基板层数的增多,使得传统的QFP等封装形式在其发展上有所限制。

我们把使用传统引线框架和封装管壳的封装技术称为引线框架式封装技,多用于如方形扁平无引脚封装(QFN)和方型扁平式封装(QFP)。

封装管壳内部结构示意图

引线框架封装工艺

使用引线框架和外部封装管壳的芯片封装制作工艺十分相似。基本流程为:首先使用充银环氧粘结剂将晶圆切片粘附于引线框架上,然后使用金属线将晶圆切片的管脚与引线框架上相应的管脚连接,再将引线框架与封装壳组合在一起,最后使用模塑包封或者液态胶灌封,以保护晶圆切片、连接线和管脚不受外部因素的影响。

引线框架主要性能

半导体封装引线框架大多采用铜材或铁镍合金(A42)两种材质,在封装中,引线框架主要有如下作用:

引线框架封装中引线的功能

良好的导电性能

引线框架在塑封体中主要作用是芯片的功能通过引线与框架上的外引脚连接,集成电路芯片还常用引线将芯片的地线连接到框架的底座上,所以,要求引线框架有良好的导电性。

良好的导热性

产品在使用时,芯片会产生热量,特别是大功率产品,工作电流较大,产生的热量更大。热量主要通过引线框架和塑封料向外散热。如果散热性能不好,则可能“烧坏”芯片。PN结一般设计温度为150℃,温度过高,可能在工作中造成PN结热击穿。大功率产品的引线框架个别还设计有专门的散热片以提高引线框架的散热能力。

良好的热膨胀匹配性

在塑料封装体中,引线框与芯片之间通过银胶进行物理连接,还与塑封料直接接触,在产品塑封、回流焊及使用中,受热时各种材料均会膨胀,所以,要求各种材料间要有良好的热膨胀匹配性。

良好的结合强度

引线框架与芯片通过银胶连接,与塑封树脂直接接触。在生产过程及使用中不可避免的要受热,各种材料间的热膨胀虽然尽可能的匹配,但总会有热应力存在。所以要求引线框架与各材料之间要有良好的结合强度。

引线框架封装(如SO、QFP、QFN)仍然是I/O小于200的半导体中最常见的。模具通常采用金属丝连接,封装也很简单,虽然使用倒装芯片、多模和模/无源组合的变体也在批量生产中。

陶瓷封装在很大程度上可以被看作是遗留技术。虽然它们过去在IC上很常见,但现在几乎只用于军事和航空电子等高可靠性应用,不愿在封装技术上做出改变。

嵌入式芯片(Embedded Component Packaging EPC),封装与大多数封装类型并不相同。一般来说,在许多集成电路封装中,器件位于基板的顶部,基板充当器件与封装板间“桥梁”的角色。“嵌入式封装”一词有着不同的含义,在嵌入式芯片封装的世界中,指采用多步骤制造工艺将元器件嵌入到基板中。

单芯片、多芯片、MEMS或无源元器件均可以并排式(side-by-side)方式嵌入到有机层压基板(Organic Laminate Substrate)之中。这些元器件均通过镀铜的通孔(via)连接起来。总而言之,通过嵌入式封装,就可以释放系统中的空间。在TDK的工艺中,器件被嵌入四个极薄的基板叠层中,以微互连和通孔为主要特点,总高度为300µm。

封装尺寸是将有源芯片嵌入基板中的驱动因素。在‘x’和‘y’轴上,会显著地整体收缩。当考虑版图布线更大化时,这种微型化可让设计多一些灵活性。如今嵌入式有源元器件的市场,主要围绕着功率模拟器件领域。蓝牙无线模块(Bluetooth WiFi modules)的微型化特点,已成为嵌入式芯片封装的主要应用领域。其他应用还包括手机市场的射频模块。

嵌入式封装的优劣势

通常情况下,IC会被封装在电路板上,但这样有时会占用系统中宝贵的电路板空间,因此考虑把芯片嵌入到基板中以节省空间和成本,这就是嵌入式芯片封装的用武之地,并不会与晶圆级封装中的扇出型封装相混淆。

扇出型封装中,裸片会被嵌入到环氧模压树脂(molded epoxy compound)填充的重新建构晶圆(reconstituted wafer)中。嵌入式芯片封装是不同的。这些元器件被嵌入到多层基板中,IC会被嵌入基板的核心部位。核心部位是用特殊的树脂做的,其他基板层均是标准的PCB材料。裸片通常是并排放置的,如果是标准的4层基板,所有裸片都会被放置于2层与3层之间,且裸片不会堆叠。

嵌入式封装的主要优点有:促进尺寸微型化、互连可靠、性能更高,并改善了对集成元器件的保护。ECP还支持模块化的趋势,通过降低其他封装技术的成本来实现。隐身的电子器件(嵌入式芯片)可有效防止逆向工程和造假。

嵌入式封装也有缺点。由于它结合了用于先进封装和印刷电路板(PCB)的技术,因此面临一些制造方面的挑战。此外,生态系统还相对不成熟。嵌入式芯片的成本仍然过高,且有时良率太低。

嵌入式封装是将多个芯片集成到单个封装体中的几种方法之一,但并不是唯一选择。系统级封装是最受欢迎的选择,但由于成本原因,扇出型封装也有很大的发展潜力。正是这些封装解决方案为市场提供价格更低、技术更好的解决方案。

嵌入式封装分类

基板从材料上可分为有机基板和无机基板两大类;从结构上可分为单层(包括挠性带基)、双层、多层、复合基板等。多层基板包括通用制品(玻璃-环氧树脂)、积层多层基板、陶瓷多层基板、每层都有埋孔的多层基板。

陶瓷基板

陶瓷基板是基于氧化铝、氮化铝和其他材料制成。基于陶瓷基板的封装通常用于表面贴装器件(surface-mount devices)、CMOS图像传感器和多芯片模块(Multi-chip Module)。

有机层压基板

有机层压基板通常用于2.5D/3D、倒装芯片和系统级封装(SiP)中,这类封装的器件位于基板之上。有机基板的材料通常是FR-4或其他材料。FR-4是一种由环氧树脂组成的玻璃纤维布。这些基板使用类似或相同的材料作为PCB。所以在某些圈子里,有机基板有时就被称为PCB。有机基板也是多层技术,其中至少有两层有机层被金属层隔开。金属层在封装中充当电迁移阻挡层(electromigration shield)。

有机基板封装(BGA,CSP)使用小型刚性(有时弯曲)基板,其上的模具是金属丝粘结或倒装芯片。大多数这样的封装使用一组球或地与主机PCB接口。一个允许这些包容纳多达4000个外加I/O!

覆晶(倒装)技术FC

覆晶技术是一种裸芯片组装技术,TFT-LCD驱动芯片常用的COF封装可以认为是典型的覆晶案例。在传统微电子组装技术中,芯片一般使用外部封装壳,芯片通过线焊方式与封装壳连接,芯片一般以晶背朝下,管脚朝上的方式放置。将封装壳与PCB板焊接后,这一放置方式延续不变,即芯片的晶背靠近PCB板。但是,在覆晶技术中芯片不需要与外部封装壳进行线焊,转而使用焊接方式将芯片与封装壳或PCB板相连,所以芯片的晶背朝上,管脚朝向PCB板,因此与传统方式中芯片的放置方式相反,故被称为覆晶,也称为倒装。

基板芯片连接技术COB

基板芯片连接技术(Chip on Board,COB)是一种常用的裸芯片组装形式。在实际应用案例中,COB形式大量出现于芯片早期试验阶段及低端产品中。由于某些芯片功能较单一,所需的输入输出管脚数较少,使用COB方式可以节省封装成本,最典型的例子应属手机SIM卡。

COB制作时一般先将晶圆切片粘贴在目标板表面,然后采用Wire bonding的方式将晶圆切片的管脚与目标板上相应的管脚连接。制做完成后将芯片、金属连接线、目标板上的管脚均用液态胶覆盖,用以隔离外界污染和保护线路。由于COB方式直接将晶圆切片组装在PCB板上,使得采用该种方式的PCB板损坏后不可维修,且COB方式组装工序较多,使用较为不便。基于上述原因,裸芯片组装技术在应用中多以覆晶技术为主。

COF/COG

在塑料封装体中,引线框与芯片之间通过银胶进行物理连接,还与塑封料直接接触,在产品塑封、回流焊及使用中,受热时各种材料均会膨胀,所以,要求各种材料间要有良好的热膨胀匹配性。

晶圆级封装技术WLP

晶圆级封装是裸芯片封装的主要技术之一,主要涉及扇入型(fan-in)和扇出型(fan-out)两种封装类型。WLP封装时裸片还在晶圆上。一般来说,WLP是一种无基板封装。WLP利用由布线层(routing layers)或重新布线层(RDL)构成的薄膜来代替基板,该薄膜在封装中提供电气连接。RDL不会直接与电路板连接。相反,WLP会在封装体底部使用锡球,从而将RDL连接到电路板。

裸芯片封装/组装

目前伴随芯片功能的提升,芯片的工作频率大幅增加。从MHz到GHz,芯片的工作频率有了质的飞跃。芯片对外围电路的要求也越严苛。微秒,纳秒级的延迟都会使数据传输出现严重错误。如何消除信号在外部电路传输时的延迟效应是设计人员不能回避的问题。

在传统封装中晶圆切片与封装壳的连接方式会引入新的负面因素—Wire bonding金属线和封装壳引脚,过长的信号线会使信号传输时受寄生RC的影响出现延迟,同时也易受到干扰。而使用裸芯片技术减少了芯片传输线的长度,从而使芯片信号的延迟大大减少。裸芯片技术在减小封装体体积的同时,还将大大提高信号传输品质,这也是与其他封装技术相比裸芯片封装技术的重要优势。但是,裸芯片技术由于在封装中没有封装壳的保护,芯片晶背暴露在外,存在被损坏的风险。所以裸芯片虽然能在绝大多数应用领域取代传统封装形式的芯片,但是绝对不能百分之百点对点可代替。现有的芯片封装技术在面对封装尺寸进一步缩小,封装成本进一步下降的需求时,有些力不从心。在现有封装技术中晶圆切片的实际尺寸已经很小,制约封装尺寸缩小的因素是封装方式本身(即便是使用CSP封装,封装比为1.14,仍然有14%的空间被浪费)。而适时引入裸芯片技术则可很好的解决上述问题。

若将裸芯片组装于新的封装基材上,则称为裸芯片封装,若将裸芯片直接组装在PCB板上,则称为裸芯片组装。裸芯片封装/组装是指在芯片与目标板(封装基板或PCB板)的连接过程中,裸芯片为原始的晶圆切片形式,芯片没有经过预先的封装而直接与目标板连接。

引入裸芯片封装,可以减少由封装壳产生的额外的体积,将标准的半导体封装芯片直接更换成无封装的裸芯片,可使研发人员直接获得该芯片理论上的最小尺寸,从而提高PCB板布线空间的利用率。如图中所示,18M的同步SRAM在使用不同的封装形式时,至少可以节省70%的空间。

裸芯片封装是一个独特的类别,包括COB(主板芯片:直接连接到主PCB上的芯片线编解码器)和COF/COG(Flex或玻璃上的芯片),后者是将芯片直接翻转到显示器的玻璃或弯曲电路上。

晶圆级封装(WLP)

晶圆级封装(WLP)就是在封装过程中大部分工艺过程都是对晶圆(大圆片)进行操作,对晶圆级封装(WLP)的需求不仅受到更小封装尺寸和高度的要求,还必须满足简化供应链和降低总体成本,并提高整体性能的要求。

封装基板(Package Substrate)是由电子线路载体(基板材料)与铜质电气互连结构(如电子线路、导通孔等)组成,其中电气互连结构的品质直接影响集成电路信号传输的稳定性和可靠性,决定电子产品设计功能的正常发挥。封装基板属于特种印制电路板,是将较高精密度的芯片或者器件与较低精密度的印制电路板连接在一起的基本部件。

20世纪初期,“印制电路”的概念被Paul Eisler首次提出,并研制出世界上第一块印制电路板(Printed Circuit Board,PCB)。集成电路封装基板是随着半导体芯片的出现而从印制电路板家族中分离出来的一种特种印制电路板,其主要功能是构建芯片中集成电路与外部电子线路之间的电气互连通道。

封装基板作为载体结构起到保护芯片中半导体元器件的作用;实现芯片中集成电路功能模块电子线路与外部功能元器件之间的电气连接;为芯片功能组件提供支撑体与散热通道;为其他电子元器件搭载提供组装平台。此外,封装基板可实现集成电路多引脚化、封装产品体积缩小、电性能及散热性改善、超高密度或多芯片模块化等目的。

当前封装基板可以简单的理解为是具有更高性能或特种功能的PCB,是可为芯片、电子元器件等提供电气连接、保护、支撑、散热、组装等功效,以实现多引脚化,缩小封装产品体积、改善电气性能及散热性、超高密度或多芯片模块化以及高可靠性的电子基板。

1989-1999

第一发展阶段:是有机树脂封装基板初期发展的阶段,此阶段以日本抢先占领了世界半导体封装基板绝大多数市场为特点;

2000-2003

第二发展阶段:是封装基板快速发展的阶段,此阶段中,我国台湾、韩国封装基板业开始兴起,与日本逐渐形成"三足鼎立"瓜分世界封装基板绝大多数市场的局面。同时有机封装基板获得更加大的普及应用,它的生产成本有相当大的下降;

2004年以后

第三发展阶段:此阶段以FC封装基板高速发展为鲜明特点,更高技术水平的MCP(多芯片封装)和SiP(系统封装)用CSP封装基板得到较大发展。世界整个半导体封装基板市场格局有较大的转变,中国台湾、韩国占居了PBGA封装基板的大部分市场。而倒装芯片安装的BGA、PGA型封装基板的一半多市场,仍是日本企业的天下。

封装是指构成“体”的过程(packaging)。即通过封装(如将可塑性绝缘介质经模注、灌封、压入、下充填等),使芯片、封装基板、电极引线等封为一体,构成三维的封装体,起到密封、传热、应力缓和及保护等作用。此即狭义的封装。封装技术就是指从点、线、面到构成“体或块”的全部过程及工艺。

实装

实装此词来自日文,此处借用。“块”搭载在“板”上称为实装,裸芯片实装在模块基板(BGA基板、TAB基板、MCM基板)上可分别构成BGA、TAB、MCM封装体,称其为一级封装(或微组装);DIP、PGA等采用引脚插入方式实装在PCB上;QFP、BGA、CSP、TBA等采用表面贴装方式实装在PCB之上,称其为二级封装;裸芯片也可以直接实装在PCB上,如COB、COF等,在此一级封装、二级封装合二为一。

即实装专指上述的“块”搭载在基板上的连接过程及工艺,涵盖常用的插入、插装、表面贴装(SMT)、安装、微组装等。模块:与下面将要涉及的“板”可以看成是多维体。带有引线端子的封装体即为“块”,进行裸芯片安装的芯片也可以看成块。

安装

板是搭载有半导体集成电路元件,L、C、R等分立器件,变压器以及其他部件的电子基板即为“板”。安装即将板(主板或副板)通过插入、机械固定等方式,完成常规印制电路板承载、连接各功能电子部件,以构成电子系统的过程称为安装。

装联

装联将上述系统装载在载板(或架)之上,完成单元内(板或卡内)布线、架内(单元间)布线以及相互间的连接称为装联。

封装基板是可为芯片、电子元器件等提供电气连接、保护、支撑、散热、组装等功效,以实现多引脚化,缩小封装产品体积、改善电气性能及散热性、超高密度或多芯片模块化以及高可靠性的电子基板。

封装基板可以简单的理解为是具有更高性能或特种功能的PCB或薄厚膜电路基板。封装基板起到了芯片与常规印制电路板(多为母板、副板,背板等)的不同线路之间的电气互联及过渡作用,同时也为芯片提供保护、支撑、散热、组装等功效。

PWB和PCB

PWB(printed wiring board,印制线路板):泛指表面和内部布置有导体图形的绝缘基板。PWB本身是半成品,作为搭载电子元器件的基板而起作用。通过导体布线,进行连接构成单元电子回路,发挥其电路功能。PCB(printed ciruid board,印制电路板)是指搭载了电子元器件的PWB的整个基板为印制电路板。在多数情况下,通常将PWB与PCB按同义词处理而不加区分。实际上PWB和PCB在有些情况下是有区别的,例如,PCB有时特指在绝缘基板上采用单纯印刷的方式,形成包括电子元器件在内的电路,可以自成一体;而PWB更强调搭载元器件的载体功能,或构成实装电路,或构成印制电路板组件。通常简称二者为印制板。

主板

主板:又称为母板。是在面积较大的PCB上安装各种有源、无源电子元器件,并可与副板及其它器件可实现互联互通的电子基板。通讯行业一般称其为背板。

载板

载板:承载各类有源、无源电子器件、连接器、单元、子板及其它各式各样的电子器件的印制电路板。如封装载板、类载板、各种普通PCB及总装板。

类载板

类载板(SubstrateLike-PCB,简称SLP):顾名思义是类似载板规格的PCB,它本是HDI板,但其规格已接近IC封装用载板的等级了。类载板仍是PCB硬板的一种,只是在制程上更接近半导体规格,目前类载板要求的线宽/线距为≤30μm/30μm,无法采用减成法生产,需要使用MSAP(半加成法)制程技术,其将取代之前的HDIPCB技术。即将封装基板和载板功能集于一身的基板材料。但制造工艺、原材料和设计方案(一片还是多片)都还没有定论。类载板的催产者是苹果新款手机,在2017年的iPhone8中,首度采用以接近IC制程生产的类似载板的HDI板,可让手机尺寸更轻薄短小。类载板的基材也与IC封装用载板相似,主要是BT树脂的CCL与ABF*树脂的积层介质膜。

多层板:随着LSI集成度的提高、传输信号的高速化及电子设备向轻薄短小方向的发展,仅靠单双面导体布线已难以胜任,再者若将电源线、接地线与信号线在同一导体层中布置,会受到许多限制,从而大大降低布线的自由度。如果专设电源层、接地层和信号层,并布置在多层板的内层,不仅可以提高布线的自由度而且可防止信号干扰和电磁波辐射等。此要求进一步促进了基板多层化的发展,因此,PCB集电子封装的关键技术于一身,起着越来越重要的作用。可以说,当代PCB是集各种现代化技术之大成者。

HDI基板

HDI基板:一般采用积层法(Build-up)制造,积层的次数越多,板件的技术档次越高。普通的HDI板基本上是1次积层,高端HDI采用2次或以上的积层技术,同时采用叠孔、电镀填孔、激光直接打孔等先进PCB技术。高端HDI板主要应用于4G手机、高级数码摄像机、IC载板等。

在电子封装工程中,电子基板(PCB)可用于电子封装的不同层级(主要用于1~3级封装的第2~5层次),只是封装基板用于1、2级封装的2、3层次,普通PCB用于2、3级封装的3、4、5层次。但是它们都是为电子元器件等提供互联、保护、支撑、散热、组装等功效,以实现多引脚化,缩小封装产品体积、改善电气性能及散热性、超高密度或多芯片模块化以及高可靠性为目的。

主板(母板)、副板及载板(类载板)常规PCB(多为母板、副板,背板等)主要用于2、3级封装的3、4、5层次。其上搭载LSI、IC等封装的有源器件、无源分立器件及电子部件,通过互联构成单元电子回路发挥其电路功能。

随着电子安装技术的不断进步与发展,电子安装各阶层的界限越来越不清晰,各阶层安装的交叉、互融,此过程中PCB的作用越来越重要,对PCB及其基板材料在功能、性能上都提出了更高、更新的要求。

20世纪80年代以后,新材料、新设备的广泛应用,集成电路设计与制造技术按照“摩尔定律”飞速发展,微小敏感的半导体元件问世,大规模集成电路与超大规模集成电路设计出现,高密度多层封装基板应运而生,使集成电路封装基板从普通的印制电路板中分离出来,形成了专有的集成电路封装基板制造技术。

目前,在常规PCB板的主流产品中,线宽/线距50μm/50μm的产品属于高端PCB产品了,但该技术仍然无法达到目前主流芯片封装的技术要求。在封装基板制造领域,线宽/线距在25μm/25μm的产品已经成为常规产品,这从侧面反映出封装基板制造与常规PCB制造比,其在技术更为先进。封装基板从常规印制电路板中分离的根本原因有两方面:一方面,由于PCB板的精细化发展速度低于芯片的精细化发展速度,导致芯片与PCB板之间的直接连接比较困难。另一方面,PCB板整体精细化提高的成本远高于通过封装基板来互连PCB和芯片的成本。

目前,在封装基板行业还没有形成统一的分类标准。通常根据适用基板制造的基板材料、制作技术等方面进行分类。根据基板材料的不同,可以将封装基板分为无机封装基板和有机封装基板。无机封装基板主要包括:陶瓷基封装基板和玻璃基封装基板。有机封装基板主要包括:酚醛类封装基板、聚酯类封装基板和环氧树脂类封装基板等。根据封装基板制作方法不同,可以将封装基板分为有核(Core)封装基板和新型无核(Coreless)封装基板。

有核封装基板在结构上主要分为两个部分,中间部分为芯板,上下部分为积层板。有核封装基板制作技术是基于高密度互连(HDI)印制电路板制作技术及其改良技术。

无核基板,也叫无芯基板,是指去除了芯板的封装基板。新型无核封装基板制作主要通过自下而上的电沉积技术制作出层间导电结构—铜柱。它仅使用绝缘层(Build-up Layer)和铜层通过半加成(SemiAdditive Process,缩写为SAP)积层工艺实现高密度布线。

优势

薄型化;

电传输路径减小,交流阻抗进一步减小,而且其信号线路有效地避免了传统有芯基板上的PTH(镀铜通孔)产生的回波损耗,这就降低电源系统回路的电感,提高传输特性,尤其是频率特性;

可以实现信号的直接传输,因为所有的线路层都可以作为信号层,这样可以提高布线的自由度,实现高密度配线,降低了C4布局的限制;

除部分制程外,可以使用原来的生产设备,且工艺步骤减少。

劣势

没有芯板支撑,无芯基板制造中容易翘曲变形,这是目前最普遍和最大的问题;

层压板破碎易于发生;

需要引进部分针对半导体封装无芯基板的新设备。因此,半导体封装无芯基板的挑战主要在于材料与制程。

封装基板的主要功能是实现集成电路芯片外部电路、电子元器件之间的电气互连。有核封装基板可以分为芯板和外层线路,而有核封装基板的互连结构主要包括埋孔、盲孔、通孔和线路。无核封装基板的互连结构则主要包括铜柱和线路。无核封装基板制作的技术特征主要是通过自下而上铜电沉积技术制作封装基板中互连结构—铜柱、线路。相比于埋孔和盲孔,铜柱为实心铜金属圆柱体结构,在电气传输方面性能更加优良,铜柱的尺寸也远低于盲孔的尺寸,直接在40μm左右。

主要的积层精细线路制作方法

半导体封装基板层间互联、积层精细线路制作方法是从高密度互联/积层多层(High Density Interconnection/Build up Multilayer,HDI/BUM)衍生而来,HDI/BUM板制造工艺技术种类繁多,通过可生产性、可靠性和成本等各方面的优胜劣汰和市场选择,目前比较成熟的工艺集中在3-5种。

早期的集成电路封装基板由于封装芯片I/O数有限,其主流制作技术是印制电路板制造通用技术—蚀刻铜箔制造电子线路技术,属于减成法。IC设计趋势大致朝着高集成化、快速化、多功能化、低耗能化及高频化发展,对应的半导体封装基板呈现出“四高一低”的发展趋势,即高密度布线、高速化和高频化、高导通性、高绝缘可靠性、低成本性。

在近年的电子线路互连结构制造领域,相比于蚀刻铜箔技术(减成法),半加成法主要采用精确度更高、绿色的电沉积铜技术制作电子电路互连结构。近十几年来,在封装基板或者说整个集成电路行业,互连结构主要是通过电沉积铜技术实现的,其原因在于金属铜的高性能和低价格,避免了蚀刻铜流程对互连结构侧面蚀刻,铜的消耗量减少,互连结构的精细度和完整性更好,故电沉积铜技术是封装基板制作过程中极其重要的环节。

积层图形制作方法:

HDI

常规的HDI技术线路制作是靠减成法(蚀刻法)完成,改良型HDI技术主要是采用半加成法(电沉积铜技术)同时完成线路和微孔制作。

减成法

减成法(Subtractive),在敷铜板上,通过光化学法,网印图形转移或电镀图形抗蚀层,然后蚀刻掉非图形部分的铜箔或采用机械方式去除不需要部分而制成印制电路PCB。

加成法

加成法(Additive),在绝缘基材表面上,有选择性地沉积导电金属而形成导电图形的方法。

半加成法

半加成法(Semi-Additive Process,SAP),利用图形电镀增加精细线路的厚度,而未电镀加厚非线路区域在差分蚀刻过程则快速全部蚀刻,剩下的部分保留下来形成线路。

高密度互连(HDI)封装基板制造技术是常规HDI印制电路板制造技术的延伸,其技术流程与常规HDI-PCB板基本相同,而二者的主要差异在于基板材料使用、蚀刻线路的精度要求等,该技术途径是目前集成电路封装基板制造的主流技术之一。由于受蚀刻技术的限制,HDI封装基板制造技术在线路超精细化、介质层薄型化等方面遇到了挑战,近年出现了改良型HDI封装基板制造技术。

根据有核封装基板的结构,把HDI封装基板制作技术流程主要分为两个部分:一是芯层的制作;二是外层线路制作。改良型HDI封装基板制造技术主要是针对外层线路制作技术的改良。

基于磁控溅射种子层的电沉积互连结构是一条全新的封装基板制造技术途径,该制作技术被称为改良型半加成法。此外,由于该技术途径不像HDI技术需要制作芯板,因此被称为无核封装基板制作技术。

无核封装基板制作技术不需要蚀刻铜箔制作电子线路,突破了HDI途径在超精细线路制作方面存在的技术瓶颈,成为高端封装基板制造的首选技术。另外,该技术采用电沉积铜制作电气互连结构,故互连结构的电沉积铜技术已经是无核封装基板制作的核心技术之一。

封装技术应用的演进

即使是最古老的封装技术今天仍然在使用。但是,通过从线键到倒装芯片外围设备再到阵列封装、缩小I/O间距、更小的封装体和多组件模块,以实现更高密度封装是明显的趋势。

晶圆制造和封装材料主要包括引线框架、模封材料(包封树脂、底部填充料、液体密封剂)、粘晶材料、封装基板(有机、陶瓷和金属)、键合金属线、焊球、电镀液等。

在大约2500亿套集成电路封装中,1900亿套仍在使用铜线键合技术,但倒装芯片的增长速度快了3倍。1500亿套仍在使用铅框架,但有机基质和WLCSP的增长速度快了三倍。只有约800亿半导体封装是基于有机基板,有机封装基板市场大约80亿美元,相当于整个PCB行业的13%。

2011-2016年的市场下行

直到几年前,封装基板市场实际上处于景气度下行的阶段。自上世纪90年代以来,随着有机封装基板在更多I/O应用中取代铅框架和陶瓷封装,该市场持续增长,2011年达到约86亿美元的峰值,并在2016年开始稳步下滑,2016年仅达到66亿美元。这种下降的部分原因是由于个人电脑和移动电话市场进入了成熟期,停滞不前的出货量和组件和集成封装降低了对先进封装包的需求。更重要的是向更小系统的全面推进,这需要从更大的线结合PBGA到更小的FCCSP的转变。这减少了单位封装基板使用的面积,而且这种转变也要求每个基板具有更高的路阻密度,以允许更紧密的倒装芯片互连。封装基板的另一个重要的不利因素来自WLCSP的流行,尤其是在智能手机中。当较小的WLCSP取代引线框封装时,较大的WLCSP(包括扇出式WLCSP)取代了引线键合和倒装芯片CSP,从而消除了潜在的有机封装基板。

另一方面,由于供应商之间的竞争,导致封装基板市场进一步受到冲击,导致高于平均水平的价格下降。2011-2016年,封装基板市场需求的减少是由于以下原因:降低了系统和半导体的增长减少台式电脑和笔记本电脑的出货量—个人电脑历来占承印物市场的50%。2017年占27%。更小的基片和芯片组集成从更大的BGA包到更小的csp的趋势——这是我们从笔记本到平板电脑的潜在趋势。但在笔记本电脑、汽车、打印机、路由器、游戏、数字电视领域也出现了一种趋势。

2017年以来的企稳回升

封装基板市场在2017年趋于稳定,在2018年和2019年的增长速度明显快于整个PCB市场,在未来五年仍然保持超过平均增长速度6.5%。封装基板市场的好转和持续增长主要是由用于高端GPU、CPU和高性能计算应用ASIC的先进FCBGA基板需求,以及用于射频(如蜂窝前端模块)和其他(如MEMS/电源)应用的SiP/模块需求驱动的。内存封装需求,尽管它们的影响更具周期性,例如用于DRAM的FCBOC封装和用于Flash的WBCSP,也是封装基板强劲需求的驱动因素。

在高密度封装中,为了降低反射噪声、串音噪声以及接地噪声,同时保证各层次间连接用插接端子及电缆的特性阻抗相匹配,需要开发高层数、高密度的多层布线基板。

按基板的基体材料,基板可分为有机系(树脂系)、无机系(陶瓷系、金属系)及复合系三大类。一般来说,无机系基板材料具有较低的热膨胀系数,以及较高的热导率,但是具有相对较高的介电常数,因此具有较高的可靠性,但是不适于高频率电路中使用;有机系基板材料热膨胀率稍高,散热较差,但是具有更低的介电常数,且质轻,便于加工,便于薄型化。同时由于近几十年内聚合物材料的不断发展,有机系基板材料的可靠性有极大提升,因此己经被广泛应用。

目前广泛应用的有机基板材料有环氧树脂,双马来醜亚胺三嘆树脂(聚苯醚树脂,以及聚醜亚胺树脂等。

2019年封装材料市场规模在200亿美金左右,封装基板约占64%

21世纪初,封装基板已经成为封装材料细分领域销售占比最大的原材料,占封装材料比重超过50%,全球市场规模接近百亿美金。根据SEMI的统计数据,2016年有机基板以及陶瓷封装体合计市场规模达104.5亿美元,合计占比53.3%。引线框架的市场规模为34.6亿美元,占比17.6%,封装承载材料(包括封装基板和引线框架)合计市场规模约为140亿美元,占封装材料的比重达70%。而传统引线框架在其自身性能和体积的局限性,以及各种新型高端技术发展替代的趋势下,占比在17%左右波动,且随着对密度要求的提高,预计未来会逐渐减小。

根据SEMI数据,2017年全球封装材料市场为191亿美金,其中层压基板、引线框架、键合金属线、塑封料四大主要材料的占比分别为32.46%、16.75%、16.23%和6.81%,主要是SEMI统计口径发生变化。2000年到2011年之间全球封装材料的销售额是逐步增加的,而2011年至2017年封装材料的绝对销售额则出现平缓下降的态势,在190亿到200亿美金之间波动。

全球地区分布

有机封装基板市场一直很小,直到1997年英特尔开始从陶瓷基板向有机基板过渡,在基板封装的基板价值可以占封装总价值(不包括模具)的15%至35%。

目前,世界上半导体封装基板生产主要在亚洲、美国及欧洲。从产值上看,封装基板的生产地区主要是日本、韩国、中国台湾和中国大陆。2019年封装基板的市场价值为81亿美元,预计未来五年将以每年近6.5%的速度增长。其中,亚洲(主要以韩国和中国台湾为主)的占有率接近61%,日本约为26%,中国大陆13%左右,而美国、欧洲及世界其它地区占有比例则相当小。

全球载板主要制造地及主要制造商现状

根据2019年Prismark的统计数据,目前全球载板的市场容量约为81亿美元,量产公司近30家。从生产地来看,全球载板主要在韩国、中国台湾、日本和中国大陆四个地区生产(99%)。近年来中国大陆量产厂商数量增长明显,但产值仍较小;

2019年全球前十五大载板公司如下表所示。从表中可以看出,载板公司基本上都是PCB产品多元化,即非从事单一的载板业务,唯一例外的是日月光材料(仅从事BGA载板制造),主要是由于该公司的母公司从事的是封测代工服务。

起初,日本供应商主导封装基板供应链。目前日本仍以超过50%的份额主导着高端FCBGA/PGA/LGA市场,我们认为未来五年内这种情况不会有实质性变化。在所有其他封装基板类别中,中国台湾/中国大陆和韩国的供应商占据市场主导地位。

日本

长期以来,日本代表着全球高端PCB(特别载板)的制造水平和引导着全球PCB的发展方向,但近年来,由于其市场策略、价格水平,削弱了其竞争力。当前日本主要的载板制造商有Ibiden、Shinko、Kyocera、Daisho、MGC-JCI(逐步退出)、Eastern(已被韩国的Simmtech收购)等。

揖斐电Ibiden

揖斐电成立于1912年,开始从事的是碳化物的生产和销售,后逐步扩大业务,进入了电化学、住宅建材、陶瓷、电子等领域。现有员工14290名。PCB产品包括HDI、BGA和FCBGA,FCBGA技术一直称冠全球。目前揖斐电在日本、菲律宾、马来西亚、中国内地共有7个生产基地,具体为:日本岐阜县大垣市4个:大垣厂(FCBGA)、大垣中央厂(FCBGA)、青柳厂(HDI)、河间厂(FCBGA),菲律宾厂(FCBGA)、马来西亚槟榔屿厂(HDI),北京厂(HDI)。

新光电气Shinko

新光电气成立于1946年9月,现有员工4838名,归属于富士通集团,富士通占新光电气50%的股份。主要产品包括:载板(BGA和FCBGA)、引线框架、封测、电子元器件等。2018年4月,公司决定投资1.9亿美元新建载板产线扩充产能20%。2017财年,它的载板及封装营收额为849.23亿日元(约7.4亿美元,其中载板约5.6亿)。

京瓷Kyocera

京瓷成立于1959年4月,是全球领先的电子零部件(包括汽车等工业、半导体、电子元器件等)、设备及系统制造公司(信息通信、办公文档解决、生活与环保等),京瓷集团有265家公司,员工人数75940名。2017财年,整个集团的营收额为15770.39亿日元(约137亿美元)。京瓷的PCB,包括有机载板(BGA、FCBGA)、HDI、高层数板、陶瓷基板等。2017财年,它的PCB营收额约6.6亿美元,其中载板约3亿。

2006年中国台湾第一次PCB产值超过日本,居全球第一;之后在规模上,一直领跑全球的PCB产业。当前,中国台湾主要的载板制造商有Unimicron、Nanya PCB、Kinsus、ASE Material、Boardtek先丰、Subtron旭德(欣兴持股30%)、ZDT臻鼎(制造在秦皇岛)、PPt恒劲(C2iM)等。

欣兴Unimicron

欣兴成立于1990年,联电为最大股东,2001年合并群策电子、恒业电子,2002年合并鼎鑫电子,2009年合并全懋,2011年收购德国Ruwel100%的股权和日本Clover75%的股权。产品包括PCB(其中,多层板占15%、FPC占5%、HDI占35%、载板占45%)、连接器等。

目前欣兴在全球共在4个国家/地区建有13个工厂,其中台湾6个(合江厂、合江二厂生产HDI和背板,芦竹二厂、芦竹三厂生产HDI,山莺厂生产HDI、BGA和FCBGA,新丰厂生产BGA和FCBGA),中国内地5个(昆山欣兴同泰生产FPC及组装,昆山鼎鑫生产多层板和HDI,深圳联能生产HDI和背板,苏州群策生产BGA、黄石欣益兴生产多层板和HDI),日本北海道的Clover生产多层板和HDI,德国Geldern的RUWEL生产多层板和HDI。

2017财年,它的营收额为649.92亿元新台币(约22.4亿美元,其中载板约9.9亿,产值位列全球第一);在整个载板中,FCBGA占营收的53%,FCCSP占17%,一般BGA占29%。

南亚Nanya

南亚电路板原为台塑集团旗下南亚塑料的PCB事业部(始于1985年),于1997年10月独立。它的PCB产品主要包括BGA、FCBGA、HDI和多层板。它在台湾、昆山建有PCB工厂,其中,台湾工厂主要从事中高端BGA、FCBGA的生产(桃园芦竹一、二、五、六、七厂、新北市树林八厂),昆山工厂(一、二厂)主要从事多层板、HDI和中低端BGA的生产。2010年以前,南亚主要承接来自日本NGK前段的英特尔订单(南亚负责前段制程生产、NGK负责后段),NGK自2010年3月底起停止供货给英特尔后,南亚直接承接英特尔订单(于2010年6月底通过英特尔的全制程认证)。南亚电路板现有员工12072人。2017财年,它的营收额为266.23亿元新台币(约9.0亿美元,其中载板约5.9亿)。其中,FCBGA约42%,BGA约24%,HDI及其他约34%。

景硕Kinsus

景硕成立于2000年9月,为华硕投资。它的PCB产品主要包括BGA、FCBGA、HDI、FPC和多层板(其中载板占营收的80%以上)。它在台湾、苏州建有工厂,其中,台湾工厂主要从事中高端BGA、FCBGA等的生产(石磊厂BGA,清华厂FCBGA、BGA,杨梅厂FPC,新丰厂FCBGA、BGA),苏州工厂主要从事多层板、HDI和中低端BGA的生产。2017财年,它的营收额为223.35亿元新台币(约7.5亿美元,其中载板约6.2亿)。

日月光材料ASE Material

ASEMaterial(或称作ASEE,日月光电子)为全球最大的半导体封测商日月光集团旗下载板制造公司,它在台湾高雄、上海、昆山建有工厂,主要产品为BGA载板,包括BOC、FBGA、PBGA、MemoryCard、FCCSP等。2017财年,它的载板营收额约2.9亿美元。2018年3月,日月光与TDK合资15亿元新台币(约0.5亿美元)在台湾高雄正式成立日月旸电子股份有限公司(ASE Embedded Electronics);将来日月旸电子将采用TDK授权的SESUB(Semiconductor Embedded in SUBstrate)技术制造埋入式载板。

韩国的载板公司数量较多,这主要归功于近年来韩国快速发展的半导体以及消费电子产业,但单个PCB公司的规模较小。当前,韩国主要的载板制造商有SEMCO、Simmtech、Daeduck、LGInnotek、KCC(Young Poong旗下)、Cosmotech、HDS等。

SEMCO三星电机

三星电机成立于1973年,属三星集团,是全球排名前列的的电子元器件制造公司。主要业务包括PCB、积层陶瓷电容、摄像头模组、WiFi模组等。其PCB产品包括HDI、刚-挠性结合板、BGA和FCBGA,公司自2015年起全力开发PLP封装技术。目前共有5个工厂:韩国釜山厂生产HDI,刚-挠性结合板和FCBGA,韩国世宗厂生产BGA,韩国天安厂生产PLP,中国昆山厂生产HDI,越南厂生产HDI和刚-挠性结合板。2017财年,它的PCB营收额为14694亿韩币(约13.5亿美元,其中载板约6.6亿)。

Simmtech信泰

信泰成立于1987年,它的产品主要包括HDI和BGA载板。它在韩国清州、日本茅野、中国西安建有PCB工厂(韩国:HDI和BGA,日本:BGA(原Eastern工厂),西安:HDI)。2017财年它的营收额为8116亿韩币(约7.5亿美元,其中载板约5亿)。

Daeduck大德

大德成立于1965年1月,是韩国最早的PCB制造企业。旗下有两家PCB公司:Daeduck GDS和Daeduck,Daeduck GDS的产品主要包括多层板、FPC和HDI,Daeduck的产品包括高层板、HDI和载板(BGA)。它在韩国、菲律宾和中国天津建有PCB工厂。2017财年两家PCB公司的营收额合计为9686亿韩币(约8.9亿美元),其中载板约3.1亿。

中国大陆的载板起步较晚,第一家实现量产BGA载板的公司于2002年正式投产,为当时属港资美维科技集团的上海美维科技公司(后被美资TTM收购);第一家实现量产FCBGA载板的公司则于2016年2月正式投产,为属奥地利的奥特斯科技(重庆)有限公司。

台企中国大陆分公司 台资 BGA

昆山南亚、苏州欣兴、苏州景硕、秦皇岛臻鼎。

上海美维科技 美资 BGA

上海美维科技有限公司成立于1999年08月25日,注册地位于上海市。经营范围包括研究、设计、生产新型片式电子元器件,包括高密度互连(HDI)印刷板,晶片基板以及相关测试仪器,销售自产产品并提供相关技术服务。主要生产HDI板,PBGA、FPBGA、CSP载板、SiP载板和MCM载板等,封装基板。产品广泛应用于数码、集成电路、储存卡、DDR和汽车、蓝牙组件等领域。

美龙翔 港资 BGA

美龙翔微电子科技(深圳)有限公司(英文名:Substrate Technologies (ShenZhen) Limited)创建于1999年底,原由香港微电子封装科技有限公司和美国STI公司共同主办的企业,2003年4月,成为香港微电子封装科技有限公司的全资子公司。首期投资总额将近1900万美元,是国内首家专业从事微电子封装材料(基板)的研究、开发、生产和销售的高科技企业公司。公司的主要产品定位于高速、高性能IC的封装产品,广泛应用于高档嵌入式微处理器芯片、高速通讯及网络处理芯片、高速图像处理芯片、高速存储芯片等领域。产品种类包括:散热增强型BGA封装基板(EBGA substrate),倒置芯片BGA封装基板(FlipChip BGA)。

安捷利电子 港资 BGA

公司是一家专业从事柔性电路板(简称FPC)设计、制造、销售、电子元器件采购及销售及薄膜覆晶组件封装的香港上市公司,产品广泛销往日本、韩国、美国、欧洲及大中华地区。公司在中国设立了广州工厂和苏州工厂,同时分别在中国华南、华东等地设立销售办事处,并在韩国、美国和欧洲设立销售公司和销售代理,为客户提供最快捷周到的本地化服务。

2020年1月20日,买方安捷利美维电子(厦门)有限责任公司(为公司间接持有6%股权的合资公司)与卖方(迅达科技中国有限公司)及卖方的最终控股股东迅达科技公司订立股权购买协议,买方向卖方收购目标公司的全部股权,代价为5.50亿美元。目标公司为广州美维电子有限公司、上海美维电子有限公司、上海美维科技有限公司及上海凯思尔电子有限公司。

深南电路 国企 DM/RFM/FCCSP

公司成立于1984年,专注于电子互联领域,致力于“打造世界级电子电路技术与解决方案的集成商”,拥有印制电路板、封装基板及电子装联三项业务,形成了业界独特的“3-In-One”业务布局。

广州兴森快捷 民企 FCCSP/PBGA/SiP

公司的主营业务继续围绕PCB业务、军品业务、半导体业务三大业务主线开展,其中PCB业务包含样板快件、小批量板的设计、研发、生产、销售以及表面贴装;军品业务包含PCB快件样板和高可靠性、高安全性军用固态硬盘、大容量存储阵列以及特种军用固态存储载荷的设计、研发、生产和销售;半导体业务产品包含IC封装基板和半导体测试板。

珠海越亚 民企 FCCSP/FCBGA

公司成立于2006年,最早由中、以两国企业合资组建,专注于高端有机无芯封装基板的发明专利的产业化。经过不断的创新与发展,公司成为世界上首家采用“铜柱法”生产高密度无芯封装基板并实现量产的创新型企业。2012年7月31日正式由珠海越亚封装基板技术有限公司更名为珠海越亚封装基板技术股份有限公司。

公司自成立以来专注于FPC、COF柔性封装基板及COF产品的研发、生产与销售,致力于在微电子领域为客户提供全面的柔性互连解决方案及基于柔性基板技术的芯片封装方案。公司是全球极少数有完整产业链布局的厂商,是国内极少数不依赖进口封装基材,而通过自产封装基材批量制造COF柔性封装基板的厂商。

东莞康源电子 民企 DM

康源电子始建于1977年,总部位于香港。1993年在虎门建厂投产,2008年转型为外商独资,现已成为一个拥有10万平方厂房、2000名智慧员工的专业印刷电路板制造商。公司专注于高端PCB和FPC产品的工艺研发、产品制造和销售,主要产品包括高密度互连积层板、多层挠性板、刚挠性印刷电路板、封装载板、HDI和高新科技领域电路板,广泛应用于通讯、汽车、消费、工业、医疗等领域,客户遍布北美、欧洲、中国及亚太等地区。

普诺威电子 民企 DM

本公司专注于传感器、物联网、可穿戴设备、通讯、金融硬件、计算机及其他电子产品行业的印制电路板的制造与销售,本公司为主要集中在传感器、物联网、可穿戴设备、通讯、汽车类、金融硬件、计算机及其他电子产品生产企业提供技术含量较高的印制电路板。主要产品包括MEMS系列印制电路板、内埋器件系列印制电路板、贴片式麦克风印制电路板、精细线路印制电路板、光模组、常规印制电路板。

重庆奥特斯 奥地利 FCBGA

奥地利AT&S集团在中国拥有五个奥特斯集团生产工厂(莱奥本-Hinterberg(Leoben-Hinterberg),奥地利费灵(Fehring),韩国安山(Ansan),印度加古德(Nanjangud),中国(上海),中国(重庆)。奥特斯科技(重庆)有限公司于2011年注册成立,是奥特斯集团在中国设立的第二家独资企业。自2008年起,奥特斯上海工厂是全球最大的高科技HDI印制电路板制造基地。重庆项目于2011年3月启动,分三期进行建设,一期项目产品为全球领先的半导体封装载板。

目前,中国内地实现量产的BGA公司有昆山南亚、苏州欣兴、苏州景硕、秦皇岛臻鼎等台资,上海美维科技等美资,美龙翔、安捷利电子等港资,兴森快捷、深南电路、越亚、丹邦、东莞康源电子、普诺威电子等内资;实现量产的FCBGA公司则有重庆奥特斯1家。

目前仅深南电路、兴森科技、丹邦科技、珠海越亚具备封装基板生产技术,2019年5月,崇达技术收购普诺威35%股权,进军IC载板。

美国和欧洲:

在美国,目前仅剩HoneywelACI公司有实力以激光钻孔技术制造积层法多层板。未来美国将会朝着适于高档次半导体封装基板工艺的相关设备研制、开发的方向努力。欧洲地区目前有能力以激光钻孔技术生产积层法多层板的厂商有:AT&S(澳地利)、Aspoeomp(芬兰)、PPE等三家公司。

1.按基材材质分类

封装基板按基材材质可分为刚性有机封装基板、挠性封装基板和陶瓷封装基板。

PCB产品按基材柔软性分类

一般工艺(单面、双面、多层板)和积层法的多层板,多用于BGA封装产品中,占三类产品生产总量85%-88%。

刚性CSP/PBGA/FC-PGA/FC-PBGA/Cavity PBGA

以聚酰亚胺薄膜为基膜的基材,如BGA、D2BGA、T-BGA、T-CSP.μCSP等,增长快。

FilmCSP/Tape-BGA

陶瓷封装基板:氧化铝基板、氮化铝基板、低温共烧陶瓷多层基板。

CeramicPGA/BGA/CSP

2.按制造工艺分类

封装基板按照制造工艺可分为刚性基板(含陶瓷基板)、挠性基板、积层法多层基板(BUM)。

3.按性能分类

封装基板按照性能可分为:低膨胀系数(a)封装基板、高玻璃化温度(Tg)封装基板、高弹性率封装基板、高散热性封装基板、埋入元件型封装基板。

4.按应用领域分类

用于智能手机的存储模块、固态硬盘等;

用于智能手机、平板电脑穿戴式设备的传感器等;

用于智能手机等移动通信产品的射频模块;

用于智能手机、平板电脑等的基带及应用处理器等;

用于数据宽带、电信通讯、FTTX、数据中心、安防监控和智能电网中的转换模块;

封装基板产品多样化,从产值分布来看,2019年封装基板主要以FC BGA/PGA/LGA(Flip Chip Ball / Pin / Land Grid Array,倒装芯片球/针/平面栅格阵列封装基板)、FC CSP(Flip Chip Scale Packaging,倒装芯片级封装基板)、FCBOC(Flip Chip Board on Chip for DRAM,动态随机存取存储器用芯片封装基板)及WB PBGA(Wire Bond PBGA,键合塑料球栅阵列封装)WB CSP(Wire Bond Chip Scale Packaging键合芯片级封装基板),RF&Digital Module(射频及数字模块封装基板)为封装基板市场的六类主要产品。

从供给来看,2019年全球主要有5个地区生产封装基板,分别是日本、中国大陆、亚洲(除去日本和中国大陆,主要是中国台湾、韩国和其他地区)、美国和欧洲。

WB PBGA/CSP

WB(wire-bonding,引线键合封装技术),用金属丝将芯片的I/O端(内侧引线端子)与相对应的封装引脚或者基板上布线焊区(外侧引线端子)互连,实现固相焊接的过程。

PBGA(Plastic ball grid array package)塑料球栅阵列。主要用于满足200-800I/O引脚数需求。目前正持续被高端倒装芯片及低端低成本CSP封装抢占市场。

20世纪90年代末,PBGA封装之后不久出现了线键CSP封装,精细间距BGA(FBGA)和CSP是完全相同的,但在未来它将被简单地称为CSP。CSP是一种更有效的线状键合PBGA封装,具有更紧密的球间距(0.8mm及以下),因此被称为细间距BGA或FBGA。我们也可以进一步将CSP定义为:封装尺寸小于20毫米的所有基板。CSP最初是运用于较少引脚数的设备,但现在已经扩展到容纳700个I/O及以上的设备。

WBCSP用金线将半导体芯片与封装基板连接,半导体芯片的大小大于基板面积80%的产品通常被称为“WBCSP”(引线键合芯片尺寸封装)。

随着半导体市场的发展,对WBCSP的总需求继续增长。但因为高速增长的FCCSP,WBCSP市场份额逐渐减少。但对于许多I/O为20–500的设备来说,它仍是一种经济高效的方法。CSP的需求最初主要由大容量移动电话市场驱动,但如今,大多数其他便携式和非便携式应用程序都在使用CSP封装,以实现更小的尺寸和更好的电气性能。

2019年全球WBPBGA/CSP封装基板产值预计为20.07美元,占全球封装基板总产值24.66%。Prismark预计2024年全球FC BGA/PGA/LGA封装基板产值将达21.98美元,年复合增长率为1.83%。

目前PBGA基板及CSP基板的主要生产供应商有JCI(日本)、Ibiden(日本)、Samsung(韩国)、LG(韩国)及PPT等公司。在TBGA基板方面,目前日本厂商仍然占据主导地位。日本的主要供应商包括:Shinko、Hitachi Cable、Mitsui及Sumitomo等公司。

FC BGA/PGA/LGA

FC BGA/PGA/LGA全称Flip Chip Ball/Pin/Land Grid Array,倒装芯片球/针/平面栅格阵列封装基板。随着芯片集成度不断提高,其对集成电路封装要求更加严格。I/O引脚数的急剧增加,使得FC BGA/PGA/LGA广泛用于具有高复杂性的MPU(微处理器和内存保护单元)、CPU(中央处理器)和逻辑器件的封装。BGA、PGA、LGA三种封装所用封装基板相似,但它们与主板的交互方式不同。所有这些封装都使用倒装芯片互连,而不是导线连接。

2019年全球FC BGA/PGA/LGA封装基板产值预计为33.52亿美元,占全球封装基板总产值41.18%。Prismark预计2024年全球FC BGA/PGA/LGA封装基板产值将达51.86亿美元,年复合增长率为9.12%。

FCCSP/BOC

FCCSP

半导体芯片不是通过引线键合方式与基板连接,而是在倒装的状态下通过凸点与基板互连,因此而被称为“FCCSP”(Flip Chip Chip Scale Package)。倒装芯片CSP(FCCSP)包提供了一个较低的轮廓,更好的电气性能,并略高于传统的电线结合CSP包I/O。FCCSP与FCBGA的区别仅在于封装尺寸(<20mm)、填料节距(典型的CSP为<0.8mm球节距)。

由于FCCSP封装的高性能(将半导体芯片到PCB间的距离降至最低,信号损失很少,可确保高性能)和高I/O(得益于精细bump pitch,形成大量I/O应用),主要用于手机应用处理器、基带等产品封装中。

FCBOC

BOC(Board on Chip for DRAM)主要包括WBBOC和FCBOC两种。2018年以前,大多数DRAM设备都采用WBBOC封装,尤其是在2017年,三星(Samsung)推出了超过35亿个WBBOC封装。

FCBOC是指使用倒装技术的DRAM封装,三星从2015年前就开始将这项技术用于图形DDR(内存)或GDDR(显存),现在正将其用于PC应用程序中的主流DDR,2019年及以后FCBOC将逐渐完全取代WBBOC封装。

BOC的主要用户是存储器公司-三星、SKHynix和Micron,主要的基板供应商包括Simmtech、Eastern、ASE Material、Unimicron等。

2019年全球FCCSP/BOC封装基板产值预计为17.25亿美元,占全球封装基板总产值21.19%。Prismark预计2024年全球FCCSP/BOC封装基板产值将达20.60亿美元,年复合增长率为3.61%。

RF AND Digital Module射频及数字模块

Digital Module

数字模块将多个模具和其他组件被焊接或嵌入主板,从而可以包括任意数量的模块应用。迄今为止最常见的包括MEMS传感器、MEMS麦克风和摄像头模块。

用于数字模块的基板与用于BGA和CSP封装的基板相似。他们通常使用简单的两到四层基板,但现在加入了更先进的薄核组装基板设计。特别是对于许多MEMS麦克风来说,一个独特的区别是在基板中使用了嵌入式电容器和电阻箔。

主要数字模组基板供应商包括金星、Unimicron、南亚PCB、深南、森科、LG Innotek等。

RFModule

射频模块包括一系列解决方案,通常包括一个或多个有源功率器件和无源元件。RF模块常见于功率放大器(PA)和功率放大器双工器(PAD)模块,还用于WLAN/蓝牙和/或GPS的连接模块,通常使用有机封装基板。射频模块的尺寸通常为3毫米到10毫米,通常可以包含一到四个有源CMOS或砷化镓芯片,以及多达四十个分立无源元件。

2019年全球RF AND Digital Module封装基板产值预计为10.55美元,占全球封装基板总产值12.96%。Prismark预计2024年RFANDDigital Module封装基板产值将达17.10美元,年复合增长率为10.41%。

用于高性能计算的大面积FCBGA封装需求驱动封装基板需求成长

高性能计算包括传统的基于cpu的计算机,从高端桌面和笔记本电脑到领先的服务器、计算和网络应用程序三大类。

后者越来越多地使用GPU和高级内存总线来实现超级计算和Al应用程序所需的高性能。长期以来,高端CPU和GPU一直被封装在FCBGA、FCLGA或FCPGA中,它们可以通过插槽直接安装到主机的主PCB上,也可以使用中间的子卡。

在笔记本电脑中系统级的尺寸和厚度要求CPU直接安装在主机的主板上。然而,在桌面服务器和许多其他高性能计算应用程序,CPU通常以BGA或LGA包的形式提供,并通过插座或类似的连接器安装到主板上。

Intel的高端服务器CPU,包括联想服务器使用的Xeon CPU,都采用了公司的PoINT(Patch on INTerposer)技术。在英特尔的命名法中,CPU芯片被翻转到一个“补丁”上,这实际上是一个具有高路由密度的BGA基板,以适应前沿的CPU芯片。然后将此补丁安装到插入器上。Intel将补丁称为HDI(高密度互连),将插入器称为LDI(低密度互连)。在Prismark的术语中,两者都是内置的封装基板,而插入器的路由密度略低。

Al和机器学习带来了对海量数据的处理需求

英特尔的Xeon是一款传统的、但处于领先地位的CPU,它是专注应用于Al和机器学习一种新的高端处理,而这些应用使用GPU。所有的应用程序都依赖于模式识别来创建一个算法来解释大量的数据,而GPU比CPU更适合这种类型的数据处理。

自动驾驶汽车可能是这些新型人工智能应用中最具辨识度的一个。但机器学习也被用于语音识别、游戏、工业效率优化和战争。Nvidia是这些Al应用的GPU的主要供应商,该公司的Nvidia的自动驾驶汽车驱动平台是系统和组件封装实践的一个很好的例子最初用于特斯拉自动驾驶仪的驱动平台,本质上是一个小型(31x16cm的盒子)超级计算机,它可以解读汽车传感器的数据,创建出汽车周围环境的虚拟3D地图。并决定适当的行动。值得注意的是,大量数据定期上传到汽车制造商的数据中心,在那里,基于数百万英里的驾驶经验,自动驾驶算法不断改进。

这些例子的CPU和GPU是大型尺寸的FCBGA封装驱动的需求复杂的封装基板的主要例子。

有机封装基板的第二个重要增长驱动力是SiP/modules。

SiP(System-in-Package)将主动和被动元器件组合在一个包含特定功能的封装体/模块中。最突出的SiP是用于蜂窝和其他射频系统的射频模块,如功率放大器模块。前端模块和WiFi模块。其他例子包括传感器模块,如MEMS加速度计算或摄像机模块,以及电源模块,比如DC/DC转换器。大多数这样的模块使用刚性PCB基板,虽然有些使用柔性,陶瓷,或引线框载体。与上面讨论的高性能计算设备相比,IO数量很低(大多数远低于100),并且封装的球/垫的间距非常宽松(最多为1毫米)。另一方面,特别是射频模块往往有一个很多且越来越多的器件和元件,必须在模块内互连。这增加了模块基板的路由密度,增加了它的层数和设计几何形状。

新的射频模块应用是5GmmWave天线模块

用于5G智能手机和类似的5G接入设备。这种应用的高频率要求射频收发器和天线之间的近距离。因此,mmlWave天线模块被设计成将收发器和支撑组件安装在一侧,贴片天线安装在另一侧。结果是一个复杂的5-2-5基板。每个5G中使用三或四个这样的天线模块毫米波智能手机。

非射频SiP模块应用

苹果提供了有趣的推动力。从苹果手表,几乎所有的组件都装在一个大的SiP。另一个SiP的例子是用在苹果的新AirPods专业无线耳机。之前的AirPods主要使用的是安装在伸缩电路上的分立元件(还有一些更小的SiP)。新的AirPodsPro将几乎所有的组件整合到一个5x10毫米的SiP中。这个SiP非常复杂。实际上,它本身由四个SiP和一个跨接PCB组成,所有这些都组合成一个小的组件。

主SiP结合了几个WLCSP到一个3-2-3基板的顶部然后集成封装。该基板的底部支持一个额外的三个SiP(一个蓝牙SiP和两个MEMS加速计SiP)加上一个跨接PCB用于连接到AirPods Pro flex电路。蓝牙SiP本身是相当复杂的,包括蓝牙芯片和内存芯片,加上一个时钟和被动式,安装在一个6L任意层基板的两侧并覆盖成型。每年要交付数十亿个SiP/模块,比大型BGA包高出一个数量级。

封装基板的需求已经被持续使用的晶圆级CSP削弱。WLCSP发展迅速,因为他们提供了小尺寸,可以非常薄(<0.4毫米)和提供良好的球间距(0.35毫米),且不使用任何基材或载体。但WLCS广泛应用于智能手机和其他便携式产品中。然而封装基板的主要增长动力是大面积FCBGA封装和SiP。

在可实现的布线密度方面,硅的技术路线图超过了PCB。封装基板是用来提供高密度的接口之间的硅模具和更大,低密度PCB主板。但是用于高性能计算处于领先地位的CPU和GPU,即使是高密度的封装基板也不足以实现一级互连。

以5μm线和空间为例,重点是半导体工艺技术作为替代。在典型的排列中。采用半导体制造技术的中间插层,将有源模的高密度布线要求与有机封装基板的低密度能力进行转换。值得注意的是,这种封装方法仍然需要有机封装基质,它的大小和层数都在增加其中一些产品已经开始批量发货。

英特尔EMIB嵌入式硅插入器

英特尔的酷睿i7 8705G笔记本处理器实际上结合了英特尔的CPU,一个AMD的GPU和HBM内存在一个单一的FCBGA封装体。为了获得最高的性能,GPU和内存采用倒装芯片,直接安装在附近,并与硅桥芯片互连,在两个芯片之间提供高完整性的信号和电源线。英特尔CPU被单独直接放置在BGA基板上。

带有TSV的硅插接器

AMD提供一系列用于高性能计算应用的CPU和GPU,包括工作站和Al处理器。为了解决高速内存访问的需求,内存最好集成在处理器封装体中。在许多情况下,这是通过在相同的高密度封装基板上,将内存芯片翻转到CPU/GPU芯片旁边来实现的。但在前沿应用中,存储芯片是堆叠在一起的,随后安装在一个硅插接器上,该插接器也携带处理器芯片。

来源:半导体在线

半导体工程师

半导体经验分享,半导体成果交流,半导体信息发布。半导体行业动态,半导体从业者职业规划,芯片工程师成长历程。