晶圆代工厂联电今天宣布,与美商Avalanche Technology合作推出22纳米自旋转移矩磁性存储器(STT-MRAM),将应用于航天等领域。

联电前瞻发展办公室暨研究发展副总经理洪圭钧表示,与Avalanche Technology合作将独立的存储器解决方案投入生产,将有助于MRAM解决方案商业化,满足市场对持久性存储器不断提升的需求。

Avalanche Technology商务发展副总经理萨布尔(Danny Sabour)说,因为现今无所不在的感测装置以及日益升高的资料处理需求,推升了对耐磨损、高持久性存储器的需求,Avalanche Technology将加快启动提高16Gb单芯片解决方案的开发工作。Avalanche Technology是下一代垂直式自旋磁性存储器技术的领导者,已有超过300项专利和应用的组合,可应用于工业、物联网、航天等领域。

在2018年时,联电就与Avalanche Technology 宣布建立合作伙伴关系,共同开发和生产 MRAM,以取代嵌入式闪存。

根据协议条款,联华电子将提供基于联华电子 28nm CMOS 制造工艺的嵌入式非易失性 MRAM 块。这将使客户能够将低延迟、非常高性能和低功耗的嵌入式 MRAM 内存块集成到 MCU 和 SoC 中,以物联网 (IoT)、可穿戴、消费、工业和汽车电子市场为目标。

两家公司还将合作扩大到 28nm 以外,因为 Avalanche 的 CMOS 兼容性和对先进工艺节点的可扩展性能够将统一存储器(非易失性和 SRAM)块集成到下一代高度集成的 MCU 和 SoC 中。这使系统设计人员无需重新设计即可维护相同的架构和软件生态系统。

什么是STT-MRAM?

STT-MRAM是指采用自旋注入磁化反转(spin transfer torque:STT)数据擦写技术的磁存储器(MRAM)。这种存储器具有非易失性、运行速度快、擦写次数无限制等半导体存储器的理想性能。

STT-MRAM备受期待的应用是,通过替代电子设备的主存储器及缓存所使用的DRAM及SRAM,使其具备非易失性,以大幅降低功耗。这种存储器也许会改变“存储器(硬盘及NAND闪存)为非易失性、更高层级的内存(DRAM及SRAM)为易失性”的传统计算机架构。

传统型MRAM方面,美国飞思卡尔半导体(Freescale Semiconductor)已于2006年开始量产,并使其在工业设备上达到实用水平。但这种存储器存在很难通过微细化来实现大容量化的课题。原因是采用了向数据写入线通入电流并利用在其周围产生的磁场来进行数据擦写的方式。这种方式因为越实现微细化,数据擦写所需要的电流就会越大,所以无法缩小提供擦写电流的晶体管的尺寸。这成了实现微细化的瓶颈。

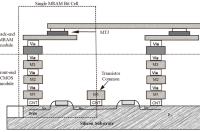

STT-MRAM存储芯片器件原理图

STT-MRAM则利用向名为MTJ(magnetoresistive tunnel junction,磁阻隧道结)的存储元件通入的电流来擦写数据。利用了在电子自旋的力矩作用下使MTJ的磁化方向发生反转的工作原理。这种方式的优势在于微细化程度越高,擦写所需要的电流越小。因此,容易通过微细化来实现大容量化,有望达到Gbit级存储容量。不过,这种存储器也存在需要克服的课题,比如元件的特性偏差会随着微细化程度的提高而增大。

其实,STT-MRAM已经开始实现商用化。飞思卡尔的MRAM部门独立出来后成立的美国Everspin Technologies就已经向市场投放了这种产品。但目前容量只有64Mbit,要扩大市场,需要实现大容量化。

2017年,我国北京航空航天大学与中国科学院微电子研究所联合成功制备国内首个80纳米STT-MRAM器件。

中国科学院微电子所集成电路先导工艺研发中心研究员赵超与北京航空航天大学教授赵巍胜的联合团队通过3年的攻关,在STT-MRAM关键工艺技术研究上实现了重要突破,在国内首次采用可兼容CMOS工艺成功制备出直径80nm的磁隧道结,器件性能良好,其中器件核心参数包括隧穿磁阻效应达到92%,可实现纯电流翻转且电流密度达到国际领先水平。

2020年,中科院微电子联合北京航空航天大学赵巍胜教授团队以及江苏鲁汶仪器有限公司,基于8英寸CMOS先导工艺研发线,自主研发原子层级磁性薄膜沉积、深紫外曝光、原子层级隧道结刻蚀以及金属互连等关键工艺模块,在国内首次实现了晶圆级亚百纳米STT-MRAM非易失性存储器件制备,为新型定制化STT-MRAM非易失性存储器的研制奠定了基础。

针对STT-MRAM存储器集成工艺中磁性薄膜沉积和刻蚀技术两大关键工艺模块研发了原子层级磁性薄膜沉积工艺并创新性地提出基于SiNx的类侧墙转移隧道结刻蚀方法,有效抑制了刻蚀过程中反溅金属沉积导致的MgO侧壁短路问题。

此外采用Ta/Ru/Ta的复合硬掩模结构,不仅有效改善了隧道结的刻蚀陡直度,还结合Trimming工艺将隧道结尺寸减小至100nm以下,一定程度上解决了漏磁场干扰问题。据了解目前组已全线打通8英寸晶圆级STT-MRAM集成工艺,实现了晶圆级STT-MRAM的存储器件制备。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。